High-performance, low-power ARM core targets SoCs

Nov 20, 2006 — by LinuxDevices Staff — from the LinuxDevices Archive — 7 viewsFaraday Technology Corp. has released a low-power, high-performance, synthesizable, 32-bit, ARM-compliant processor core for SoC (system-on-chip) designs. The FA626 clocks up to 533 MHz, is supported with a Linux port, and targets STB, DVR, IPTV, printer, WLAN, WiMax, and SAN applications, according to the fabless ASIC and chip IP provider.

The FA626 is touted as offering the benefit of ARM architecture compatibility, but with performance comparable to MIPS24K- and PowerPC 440-based processors. The core was designed for UMC's 0.13 micron HS logic process and dissipates around 0.76 mW/MHz in core logic, making it “one of the most power-efficient high-speed processors,” the company claims.

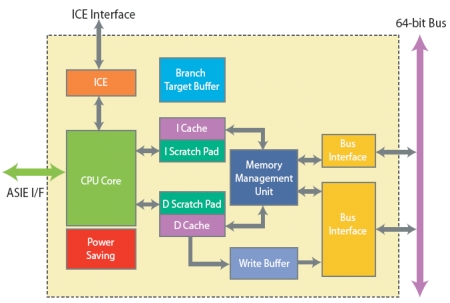

According to Faraday, the FA626 comprises a synthesized ARM v4 architecture CPU core, an MMU, 32KB/32KB instruction/data caches, and configurable scratch pads from 8KB to 32KB, in an 8-stage pipeline architecture. A single-phase clock and standard cell-based approach are said to simplify the integration of the FA626 core into application-specific SoC designs. Additionally, the company offers a variety of auxiliary IP blocks — including memory, PCI bus, Ethernet, graphics, USB, CF, SDIO, etc. — which are available for SoC designs based on the FA626.

FA626 block diagram

(Click to enlarge)

The company lists the following key features and specs for the FA626:

- CPU Core:

- ARM V4 instruction set

- High speed up to 533 MHz (Worse Case)

- 8-stage pipeline

- Branch prediction â€" static and 2-bit counter

- Single phase clock

- Memory-mapped I/O

- 32 X 32 MAC

- 32-bit AHB system bus

- Memory Management Unit:

- Enhanced ARM V4 compliant MMU

- 8-entry fully-associative ITLB

- 8-entry fully-associative DTLB

- 128-entry 2-way Unified TLB

- Hardware table walk

- Memory Subsystem:

- Instruction and data caches

- Non-blocking data cache access

- Hardware cache coherence over PVCI

- interface

- Cache lockdown

- Instruction and data scratchpads

- Miscellaneous:

- 64-bit bus interface PVCI interface

- Easy SoC integration

- Bi-endian support

- Power saving control unit

- Support standard ARM ICE interface

- Standard ARM tool chain support

- External coprocessor interface with

- application-specific instruction extension (ASIE)

Faraday says it supports the FA626 with standard ARM and GNU toolchains, plus a “modularized” development platform that includes a pre-ported Linux kernel and drivers.

Dr. George Hwang, Faraday's VP of R&D and International Business, stated that the “FA626 will open up new market applications for embedded SoC designs in favor of the ARM cores.”

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.