MIPS hardens 32-bit RISC cores, lowers costs

Sep 7, 2005 — by LinuxDevices Staff — from the LinuxDevices Archive — 3 viewsMIPS Technologies is shipping “hard” versions of two processor cores it says have achieved rapid adoption over the past year as synthesizable, “soft” cores. The 24Kc and 4KEc hard cores target system OEMs, fabless semiconductor companies, and startups, and offer lower costs and risks than synthesizable IP cores, MIPS says.

MIPS described the difference between its hard and soft core products in its 2004 annual report: “We have over 85 licensees that develop, manufacture or have manufactured and sell silicon solutions based on the MIPS processor architecture, processors, and cores. We have two major types of licensees: those that license design rights, which we refer to as synthesizable or “soft” cores, and independently develop their own MIPS compatible cores; and those that license “hard” cores from MIPS which they normally insert directly into their own integrated circuits containing other elements of their system.”

According to MIPS, both the 24Kc and 4KEc cores include the following features:

- 32-entry TLB (translation lookaside buffer) for Linux support

- MIPS16e ASE (application-specific extension) for code compression

- High-performance multiply/divide unit

- CorExtend capability to enable customer-defined instruction extensions

- COP2 interface to customer-defined coprocessor

- Instruction and data breakpoints for debug support

24Kc

The 24Kc is the base version of MIPS's 24K family, dubbed the “highest-performing 32-bit synthesizable core” when it was announced in October of 2003. MIPS shipped its 24K series in April of 2004, and claims the family has since been licensed at a rate twice that of the nearest competitor.

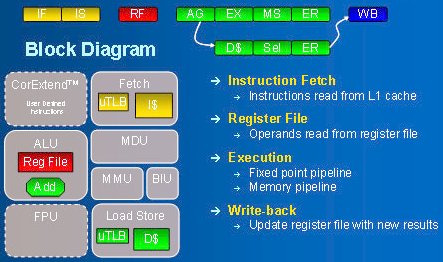

MIPS 24K core block diagram

According to MIPS, the new hard core version of the 24Kc core targets budget-conscious SoC designers — “including those in the Asia/Pacific region” — building chips for set-top boxes, residential gateways, digital TVs, and other high-end consumer applications. The core is available on a TSMC 180-nanometer G process, with a claimed worst-case frequency of 260MHz, a core size of 10.7 square millimeters, and 16KB each of instruction and data caches.

MIPS32 4KEc

The MIPS32 4KEc is a value-oriented core featuring code compression, large writeback cache memories, and extensive clock gating. MIPS says the synthesizable version can be optimized for performance or low power, and is among the most popular MIPS cores for broadband and networking applications. The synthesizable version was used by PMC-Sierra in a VoIP router-on-a-chip announced last summer.

MIPS says the hard core version of the 4KEc offers a low price-to-performance ratio for those designing SoCs for high-performance handheld and mobile consumer devices. The core is available in a TSMC 130-nanometer G process, has a claimed worst-case frequency of 233MHz, and a footprint of just 2.5 square millimeters. It includes 8KB each of instruction and data cache.

MIPS VP of Marketing Russ Bell said, “We are especially proud of the new 4KEc hard core, the first hard core developed by our new Shanghai R&D center.”

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.