PMC-Sierra readies dual-core MIPS SoC

Oct 5, 2004 — by LinuxDevices Staff — from the LinuxDevices Archive — 5 viewsPMC-Sierra plans to ship a high-end, high-integration SoC (system-on-chip) in Q2 2005 that will likely be the highest-performing MIPS chip yet. The RM11200 will deploy dual 64-bit E11K MIPS cores, along with high-speed I/O. It will target networking, storage, and communications applications such as enterprise routers, storage systems, and DSLAMs (digital subscriber line access multiplexers).

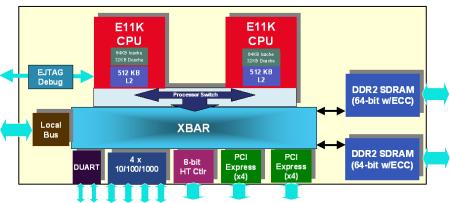

The RM11200 will be based on 90nm CMOS process technology, and will include dual 7-stage, symmetric superscalar E11K cores, said to support processor-to-processor cache coherency using the 5-state MOESI cache coherency protocol, as well as I/O coherency over each of the I/O interfaces. The E11K cores have 64KB of instruction cache and 32KB of data cache, in addition to 1MB of on-chip L2 cache. All caches uses ECC.

In addition to two E11K MIPS-64 cores, the RM11200 integrates dual 64-bit memory controllers supporting DDR2-800, a PCI Express controller supporting dual 4-lane interfaces or a single 8-line interface, and a quad Gigabit Ethernet controller with hardware-assisted checksums and eight automatically assigned queues per port. The SoC also integrates a 600MHz HyperTransport interface, said to provide up to 10Gbs of full-duplex bandwidth. And, all I/O interfaces can write directly into the L2 cache.

Block diagram of RM11200

(Click to enlarge)

The RM11200 uses a clockless interconnect technology called “xbar,” said to save power and make power consumption proportional to the amount of data being switched. Xbar can support aggregate bandwidths over 1Tbs with 3nsec port-to-port latency, PMC-Sierra claims.

Industry analyst and EEMBC president Markus Levy said, “The RM11200 will clearly be the MIPS-based performance leader.”

Availability

The RM11200 is expected to sample in Q2, 2005, and will be priced at $450 when it reaches volume production. It will ship in a 1152-pin Flip Chip BGA package, along with datasheets, application notes, a reference design, and software.

The RM11200's predecessor, the dual-core RM9K, supports embedded Linux, and both chips are said to be “100 percent compatible” with the MIPS instruction set.

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.