SAN/RAID SoC supports PCI Express, PCI-X, Linux

Oct 8, 2004 — by LinuxDevices Staff — from the LinuxDevices Archive — 4 viewsAMCC will sample an SoC (system-on-chip) for RAID and SAN (storage area networking) controllers in Q1, 2005. The 440SPe is AMCC's first product based on a 400-series PowerPC core since it acquired the series from IBM in April. MontaVista and Wasabi will support Linux and BSD, respectively, on the device.

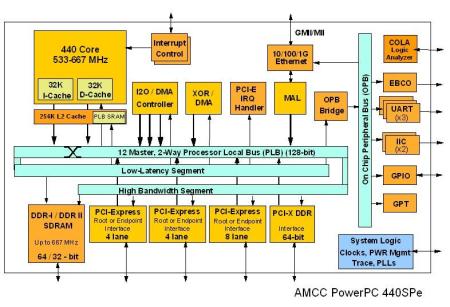

Additionally, AMCC says the 440SPe will be the first SoC to offer three independent PCI Express and one PCI-X 2.0 interfaces.

AMCC acquired the 400 series embedded PowerPC processor family from IBM in April for $227 million in a deal that also included access to IBM's SoC design methodology and advanced CMOS process technology. Tom Halfhill, a senior analyst at In-Stat/MDR, observes, “By announcing a new PowerPC chip less than six months after acquiring a significant portfolio of PowerPC intellectual property from IBM, AMCC is demonstrating its serious intent to be a major PowerPC supplier alongside IBM and Freescale.”

Halfhill adds, “The PowerPC440SPe is important in its own right, bringing the latest PCI Express interfaces to networking I/O and storage applications.”

The 440SPe

The 440SPe is based on a 533MHz to 667MHz PowerPC 440 core, a dual-issue, superscalar, 32-bit RISC CPU core based on Book E enhanced PowerPC architecture. It will include 32KB each of L1 data and instruction caches, and 256KB of L2 cache that can optionally be configured as on-chip SRAM.

AMCC 440SPe integrates three independent PCI Express interfaces, as well as PCI-X

(Click to enlarge)

Integrated peripherals and features include:

- Three PCI Express interfaces, supporting one 8-lane PCI Express upstream interface and two 4-lane downstream interfaces

- A 64-bit PCI-X interface, which operates at double data rate (DDR266), with a claimed peak bandwidth of 2.13GBps

- The PCI Express and PCI-X interfaces can function as an opaque PCI Express to PCI Express or PCI Express to PCI-X bridge, AAMC says

- CoreConnect 128-bit Processor Local Bus (PLB) implemented with a two-way crossbar architecture in which each segment has separate 128-bit read and write data buses that may operate concurrently, providing up to a claimed 10.4GBps of total on-chip bandwidth at 166MHz

- XOR acceleration, useful for speeding up the constant checksums in certain storage/RAID applications

- Integrated messaging unit, designed to meet I20 specifications

- DDR memory controller that supports DDR I 166/333 and DDR II 333/667 memory devices

- 256KB on-chip SRAM can be configured as an L2 cache or as a memory-mapped SRAM for low-latency access, ideal for storing data packets, critical code segments, Ethernet or DMA descriptors, or other application-specific data, AAMC says

- Gigabit Ethernet MAC (GENET)

- Two IIC controllers

- A host of GPIO pins

- Three UARTs

The 440SPe will be manufactured using 130nm process technology.

Wasabi Systems's marketing VP Jim Schrand said, “The PowerPC 440SPe [offers] customers a remarkable level of bandwidth and connectivity.”

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.