“cJTAG” debuts

Sep 4, 2008 — by Eric Brown — from the LinuxDevices Archive — 94 viewsA company that sells IP (intellectual property) cores to system-on-chip (SoC) designers claims to be shipping the first synthesizable IP core to implement the IEEE 1149.7 “Compact JTAG” (cJTAG) standard. cJTAG uses only two pins for I/O, clocking, and control, instead of JTAG's four, while also improving debugging, proponents say.

Championed by Texas Instruments (TI), with support from Freescale Semiconductor, Intel, ST, and other semiconductor and debug equipment manufacturers (such as Lauterbach), the cJTAG extensions use only two pins for I/O, clocking, and control instead of JTAG's four. By reducing pin-count requirements, cJTAG is said streamline development of small-format, multiple-IC system-on-chips (SoCs) used in modern embedded devices. Additionally, TI says it “standardizes power-saving conditions, simplifies manufacturing of multi-chip modules, and stacked die devices, and provides the ability to transport instrumentation data.”

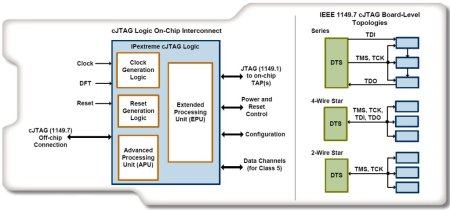

cJTAG IP core logic on-chip interconnect (left) and board-level topologies (right)

(Click to enlarge)

cJTAG is not intended to replace IEEE 1149.1 JTAG, says IPextreme. Instead, it maintains compatibility with existing JTAG-based hardware and software, while adding new capabilities. For example, it defines a new Test Access Port (TAP) called TAP.7, and said to offer increased chip integration, power management, application debug, and device programming features.

The cJTAG standard has drawn the support of a mobile device standards group called Mobile Industry Processor Interface (MIPI) Alliance. Rolf Kuhnis, Nokia's chairman of MIPI's Test and Debug working group, stated “Reducing pin count is an important technology to enable advanced mobile devices. IEEE 1149.7 is a standardized, reduced pin interface compatible with existing technologies, and [it] addresses multi-chip debug challenges. This is why IEEE 1149.7 is recommended in the MIPI test and debug specifications.”

Inside cJTAG and the new IP core

cJTAG Features are grouped into six classes, each of which is a superset of lower classes. IPextreme says its cJTAG - IEEE 1149.7 IP core supports all six classes, which include:

- Class 0 — adds support for multiple TAPs on a single chip

- Class 1 — adds support for the 1149.7 command protocol, generation of functional and test resets, and power control

- Class 2 — adds bypass of chip's system test logic, resulting in a one-bit path for Instruction Register (IR) and Data Register (DR) scans

- Class 3 — adds support for connecting TAP.7 controllers in a four-wire star topology

- Class 4 — adds support for advanced scan protocols and two-pin operation, enabling TDO and TDI to be removed or used for other functions

- Class 5 — adds support for up to two data channels for non-scan data transfers, which can be used for application-specific debug and instrumentation purposes

The IPextreme cJTAG - IEEE 1149.7 IP core package includes Verilog source code, integration testbench and tests, documentation and scripts for simulation and synthesis, and support for common EDA tools, says the company. Additional features of the core are said to include:

- Support for extended processing units (EPU) for class 0-3 operation, and advanced processing units (APU) for class 4-5 operation

- Further parameterization within EPU and APU for class-specific and optional features

- Supports separate blocks for clock and reset signal conditioning

- Supports all JScan0-3, SScan0-3, OScan0-7 and MScan scan formats

- Supports all mandatory and optional commands

- Firewall provides hot-connection capability

Stated TI's emulation technology product manager, Stephen Lau, “The IEEE 1149.7 test and debug technology will allow the electronics industry to extend IEEE 1149.1 capabilities while also providing increased functionality to their embedded designs. IPextreme's technical expertise and experience in working with semiconductor leaders makes them well-suited for this initiative.”

Stated IPextreme CEO, Warren Savage, “Our objective is to make both TI and our customers successful through the adoption of the IEEE 1149.7 standard.”

Availability

The cJTAG — IEEE 1149.7 core is available now for $75K, list price, says IPextreme. More information may be found here. IPextreme will be hosting a one-hour webinar in mid-September entitled, “cJTAG - IEEE 1149.7: The Next Generation in Test and Debug.” More details on this as yet unscheduled event may be found here.

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.