Linux-ready ARM SoCs target diverse markets

Feb 26, 2010 — by LinuxDevices Staff — from the LinuxDevices Archive — 5 viewsSTMicroelectronics says it is now shipping four Linux-ready SoCs (system on chips), based on similar ARM926EJ-S cores but targeting different market segments. The SPEAr300, 310, 320, and 600 have single or dual cores, run at up to 400MHz, and sell for as little as $7 in production quantities, the company says.

STMicroelectronics (ST) launched its SPEAr (structured processor enhanced architecture) range in 2005 with the release of the SPEAr Head200, integrating a 266MHz ARM926EJ-S core with a 200Kgate configurable logic block. The SPEAr Head600 and SPEAr Plus600 followed in 2007, using the same core and 90nm production process, but clocking up to 333MHz and sporting a 600Kgate configurable logic array.

In 2008, ST moved to a 65nm process with the SPEAr Basic, again with the 333MHz ARM926EJ-S core. This time with a 300Kgate logic array, the device was touted as facilitating custom design, thanks to a separately available development kit and an external FPGA (field programmable gate array).

ST's newly announced SPEAr300, 310, 320, and 600 use the same ARM926EJS core, and similar clock speeds — 333MHz "worst-case," or "up to 400MHz" in typical conditions. (They're still fabbed with 90nm and 65nm technology, too, according to the company, though further specifics weren't provided.) But the new SoCs omit configurable logic arrays, instead providing on-chip functionality tailor-made for different market segments.

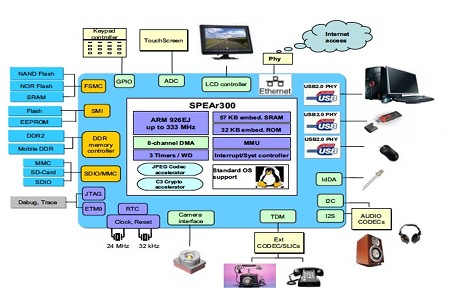

SPEAr300

For example, the new SPEAr300 targets HMI, VoiP, and security applications, according to ST. To that end, key ingredients include a camera interface, an LCD controller (resolutions up to 1024 x 768 pixels), a 9 x 9 keyboard controller, a TDM (time division multiplex) bus with 512 slots, and a cryptographic (DES/3DES/AES/SHA1) accelerator, the company says.

STMicroelectronics' SPEAr300

(Click to enlarge)

ST says the SPEAr300 has a single fast Ethernet port, USB 2.0 (2 hosts, 1 device), and interfaces including SDIO/MMC, SPI, I2C, I2S, UART, and fast IrDA. Some of the SoC's other specifications include:

- Memory:

- 32-Kbyte ROM and and up to 57-Kbyte internal QQSRAM

- LPDDR-333/DDR2-666 interface

- Serial SPI flash interface

- Flexible static memory controller (FSMC) up to QQ16-bit data bus width, supporting external SRAM, NAND/NOR flash memories, peripherals and FPGAs

- Miscellaneous functions:

- Touchscreen support

- Integrated real-time clock, watchdog, and system controller

- 8-channel 10-bit ADC, 1 MSPS

- 1-bit DAC

- JPEG codec accelerator

6 general-purpose 16-bit timers with capture mode and programmable prescaler - Up to 44 GPIOs with interrupt capability

- Package — LFBGA289 (15 x 15mm, pitch 0.8mm)

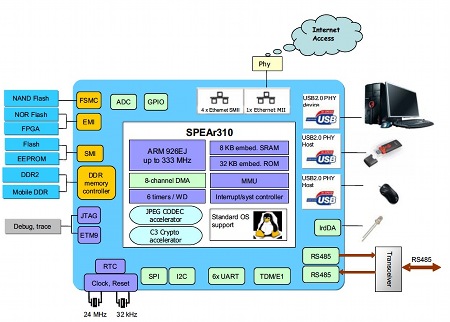

SPEAr310

ST says the SPEAr 310 is suitable for a variety of embedded applications but targets telecom in particular. Key features cited this time include six fast Ethernet ports, six serial interfaces, a 128-timeslot TDM bus, and two HDLC (high level data link control) ports.

STMicroelectronics' SPEAr310

(Click to enlarge)

According to ST, the SPEAr310 again has three USB 2.0 ports (2 hosts, 1 device), SPI, I2C, and IrDA interfaces, and a cryptographic accelerator. However, this SoC does not appear to have a LCD controller.

Some of the Spear310's other specifications include:

- Memory:

- 32-Kbyte ROM and up to 8-Kbyte internal SRAM

- LPDDR-333/DDR2-666 interface

- Serial SPI flash interface

- Flexible static memory controller (FSMC), up to 32-bit data bus width, supporting external SRAM, NAND/NOR Flash memories, peripherals and FPGAs

- Miscellaneous functions:

- Integrated real-time clock, watchdog, and system controller

- 8-channel 10-bit ADC, 1 MSPS

- JPEG codec accelerator

- 6 general-purpose 16-bit timers with capture mode and programmable prescaler

- Up to 102 GPIOs with interrupt capability

- Package: LFBGA289 (15 x 15mm, pitch 0.8mm)

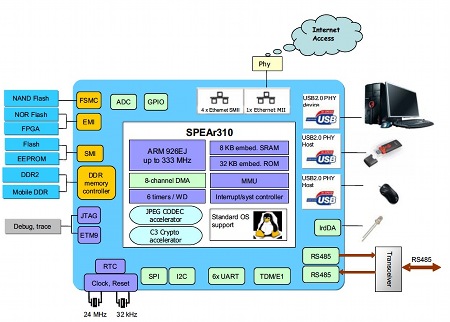

SPEAr320

ST says the SPEAr320 is intended for both factory automation and consumer applications. Key attributes this time around include a SDIO/MMC interface, two CAN interfaces, four serial ports, a parallel port, and an LCD controller (max. resolution 1024 x 768 pixels).

STMicroelectronics' SPEAr320

(Click to enlarge)

According to ST, the SPEAr320 has two Ethernet ports, three USB 2.0 ports (two host, one device), three SPI ports, plus I2S and IrDA interfaces. Like the other SPEAr3xx SoCs, the device is also said to have a cryptographic accelerator.

Some of the SPEAr320's other specifications include:

- Memory:

- 32-Kbyte ROM and up to 8-Kbyte internal SRAM

- LPDDR-333/DDR2-666 interface

- Serial SPI flash interface

- Flexible static memory controller (FSMC), up to 16-bit data bus width, supporting external SRAM, NAND/NOR Flash memories, peripherals and FPGAs

- Miscellaneous functions:

- Touchscreen support

- Integrated real time clock, watchdog and system controller

- 8-channel 10-bit ADC, 1 MSPS

- 4 PWM timers

- JPEG codec accelerator

- 6 general-purpose 16-bit timers with capture mode and programmable prescaler

- Up to 102 GPIOs with interrupt capability

- Package: LFBGA289 (15 x15 mm, pitch 0.8 mm)

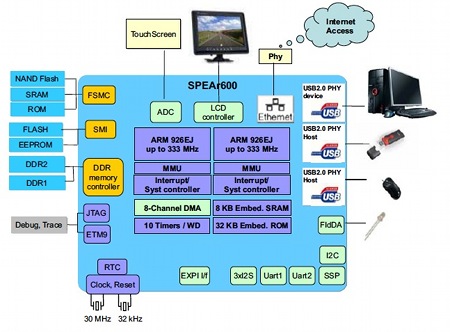

SPEAr600

Unlike the SPEAr3xx SoCs, the SPEAr600 employs dual cores, giving it performance of 733 DMIPS (Dhrystone million instructions per second) and making it suitable for "highly compute-intensive embedded applications across market segments," ST says. The device also offers external local bus access, permitting glueless FPGA connection, the company adds.

STMicroelectronics' SPEAr600

(Click to enlarge)

The SPEAr600 does not appear to have a cryptographic accelerator, but it is akin to most of the SPEAr3xx SoCs in that it features an LCD controller (again, up to 1024 x 768), a gigabit Ethernet port, three USB 2.0 ports (two host, one device), three SPI ports, and two serial ports. Here, audio is also said to be supported, via one I2S stereo input and two I2S stereo outputs.

Some of the SPEAr600's other specifications include:

- Memory:

- 32 Kbytes ROM and up to 8 Kbytes internal SRAM

- External DRAM interface: 8/16-bit DDR1-400/DDR2

- Flexible static memory controller (FSMC) supporting parallel NAND Flash memory interface

- Serial NOR Flash memory interface

- Miscellaneous functions:

- Integrated real time clock, watchdog, and system controller

- 8-channel 10-bit ADC, 1 MSPS

- JPEG codec accelerator

- 10 general-purpose 16-bit timers with capture mode and programmable prescalers

- 10 GPIO bidirectional signals with interrupt capabilities

- External 32-bit local bus

- Package: PBGA420 (23 x 23mm, pitch 1mm)

Further information

According to STMicroelectronics, the new SPEAr SoCs are available with development tools that include evaluation kits, a STLinux distribution, and flash images. More information may be found here.

General information on the SPEAr300, 310, 320, and 600, including detailed data sheets, may be found on the STMicroelectronics website, here.

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.