64-way chip gains Linux IDE, dev cards, design wins

Apr 30, 2008 — by Eric Brown — from the LinuxDevices Archive — 30 views Tilera introduced a Linux-based development kit for its scalable, 64-core Tile64 SoC (system-on-chip). The company also announced a dual 10GbE PCIExpress card based on the chip (pictured at left), revealed a networking customer win with Napatech, and demo'd the Tile64 running real-time 1080P HD video.

Tilera introduced a Linux-based development kit for its scalable, 64-core Tile64 SoC (system-on-chip). The company also announced a dual 10GbE PCIExpress card based on the chip (pictured at left), revealed a networking customer win with Napatech, and demo'd the Tile64 running real-time 1080P HD video.

(Click for larger view of TILexpress-20G card)

Announced in August, the massively parallel Tile64 SoC targets network and video devices that require significant application processing, such as surveillance systems, videoconferencing, and firewalls with deep packet inspection. Fabbed on 90nm process technology at TMSC, the Tile64 includes 64 cores, each clocked at between 600MHz and 900MHz and each containing its own L1 and L2 cache. Tilera claims that the Tile64 outperforms Intel's dual-core Xeon processor by a factor of 10, while offering 30 times better performance per Watt.

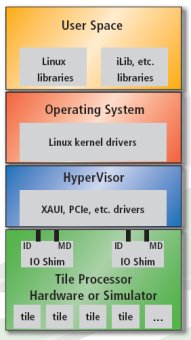

The Tile64 is based on a proprietary VLIW (very long instruction word) architecture, on which a MIPS-like RISC architecture is implemented in microcode. A hypervisor enables each core to run its own instance of Linux, or alternatively the whole chip can run Tilera's 64-way SMP (symmetrical multiprocessing) Linux implementation. An “iMesh” switching interconnect, developed by Tilera's founder, MIT professor and serial entrepreneur Dr. Anant Agarwal, is said to eliminate the centralized bus intersection that limited scalability in previous multicore designs. (See our previous coverage for an in-depth look at the Tile64.)

Tile64 architecture (smaller diagram at right

represents a single core)

(Click to enlarge)

Linux-based IDE includes SGI Pro64 compiler

MDE development environment (Click to enlarge) |

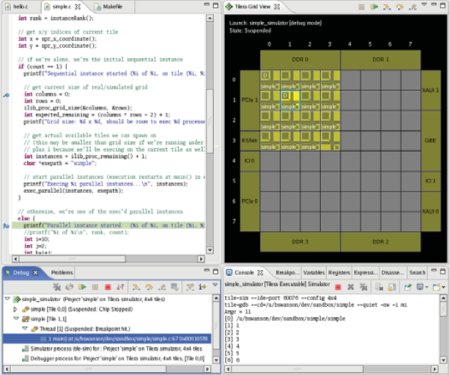

Tilera's Multicore Development Environment (MDE), now available, aims to provide a Linux development environment that is familiar, yet still capable of producing binaries that exploit the Tilera's massive parallelism. Historically, ease of programming has sometimes proven to be a challenge with massively parallel processors, such as the various GPU designs (graphical processor units) that have been used for general purpose processing through the years.

The Tilera MDE includes an Eclipse-based IDE, along with a runtime environment based on an SMP Linux 2.6 kernel. The included toolchain supports C++ development via an Edison Design Group (EDG) compiler front end and SGI's Pro64 compiler, which is in turn based on MIPSpro. The compiler provides GNU extensions, as well as features including automatic function in-lining, software pipelining, and SIMD (single instruction, multiple data, similar to Intel's MMX and sequels) intrinsics for enabling fine-grain parallelism, says the company.

The MDE also includes a parallel debugger (see image below), along with an application profiler aimed at helping developers figure out what parts of their code to optimize for multicore. The debugger offers visibility into cores, I/O, and memory, says Tilera.

Alternatively, developers can port their applications to Tilera's iLib C library, included with MDE, and aimed at exploiting parallelism while still supporting standard system calls. The approach appears to resemble that used in Intel's Threading Building Blocks, released last year under an open-source license.

Stated Richard Schooler, VP of Software Engineering at Tilera, “Over the years, customers in the embedded communications market have invested many engineering years and millions of dollars into their software. Tilera's MDE allows customers to use their existing code, leveraging their substantial investment, to get the high performance delivered by the Tile family.”

MDE's Debugger

(Click to enlarge)

A 20Gbps networking board

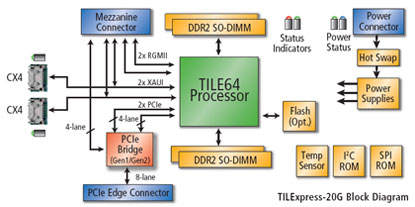

Boasting two 10Gbps Ethernet ports, the new TILexpress-20G joins the previously announced TILexpress-64, a now-shipping PCI Express card that comes with six or 12 gigabit Ethernet ports. Both cards are designed for networking and video-processing applications, and can be used in production systems with passive backplanes, or as targets in development hosts.

TILexpress-20G block diagram

Like the TILexpress-64, the 20G (pictured atop page) is an 8-lane PCIe card, but it includes dual 10Gbps Ethernet ports, offering a combined 20Gbps throughput. It is equipped with a Tile64 clocked at either 700MHz or 866MHz, plus four SODIMM memory sockets supporting up to 16GB of DDR2 RAM, as well as an optional 512MB integrated flash memory. An expansion connector enables options such as SFP+ 10GbE connections or multiple 1Gbps Ethernet.

The TILexpress-20G is capable of supporting high-speed deep packet processing, says Tilera, including intrusion prevention and virus and spam filtering. Other applications include network monitoring and forensics, enabling “bump in the wire” processing or use as a PCIe-based network interface within an embedded appliance.

At Interop, Tilera is demonstrating a prototype of the card simultaneously encoding eight real-time HD 1080P streams at 30 frames per second. No details were provided about the codec or compression format, but the company claims that to achieve similar performance, a system would require up to ten DSP chips or multiple video processors.

Napatech's forensics board

Finally, network forensics company Napatech, announced the integration of the Tile64 into its “X” family of network adaptors, which perform network performance analysis and dynamic pattern matching. In previous models, Napatech had used a combination of FPGAs (field programmable gate array) and other multicore processors, but selected Tile64, says Tilera, due to its ease of programming, 20Gbps performance, and under 20-Watt power consumption.

Napatech's new Pattern Matching Adapter is said to offer 20Gbps pattern matching with minimum-size packets, across IP fragments and packet boundaries, and to match up to a million 64-byte patterns. The Adapter is also said to sustain a million flows and to handle 100,000 new flows per second. Applications include intrusion detection, forensic analysis, lawful intercept, cyberspace surveillance, and other security applications.

Stated Erik Norup, President of Napatech, “Napatech selected the Tile64 processor because it provides the highest pattern matching performance and the lowest power consumption for a processor in its class.”

Availability

Tilera will demonstrate its MDE package, 20G board, and the real-time HD 1080P application today and tomorrow, at Interop booth 2361 at the Mandalay Bay Convention Center in Las Vegas. The Tile64 is available now, in three variants differentiated by I/O mix and clock. Pricing starts at $435 in 10,000 quantities. The MDE is available now, and the TILExpress-20G is currently sampling, with production targeted for the third quarter. Pricing for the 20G and the MDE were unavailable.

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.