Customizable ARM-based SoC boasts Linux support

Mar 28, 2005 — by LinuxDevices Staff — from the LinuxDevices Archive — viewsFaraday Technology has released a customizable SoC (system-on-chip) in its application-specific “structured ASIC” product family. The PeripheralComposer-1 (PC-1) is based on an ARM processor core, integrates USB and Ethernet, and is supported by a comprehensive set of software and hardware development tools, including Linux, according to the company.

In addition to providing the functions of an interface-oriented, ARM-based SoC, the PC-1 implements a large, “flexible” and “structured” ASIC region that enables the addition of customer-specific functions. According to Faraday, the PC-1 base array also includes a number of IP blocks that are “essential to data networking and system interconnection.” The base array is pre-verified and pre-manufactured, significantly reducing customers' design and manufacturing time, the company adds.

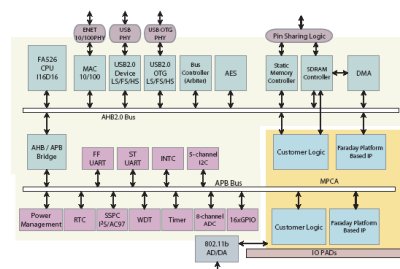

Peripheral Composer-1 Block Diagram

(Click image for larger view)

Key features included in the base array, according to Faraday, are:

- Processor:

- 190 MHz 32-bit ARMv4 instruction set

- Memory management unit

- 16KB instruction cache, 16KB data cache

- JTAG ICE

- Memory Controllers:

- Static memory controller supports SRAM, and Flash

- SDRAM controller

- Encryption Engine:

- DES / Triple-DES / AES encryption and decryption compliant with NIST standard

- AES 128/192/256-bit keys

- 10/100 Ethernet MAC and PHY

- USB 2.0 OTG controller and PHY

- USB 2.0 device controller and PHY

- 8-channel 10-bit 200K sample/second ADC

- 802.11b wireless LAN modem (optional)

- Other Peripherals:

- Power Management

- 5 I2C Cores

- SSP

- 2 UARTs

- RTC, Timer, Watchdog Timer, Interrupt Controller

The custom logic consists of 1 million MPCA (Metal Programmable Cell Array) gates and 60 KB of memory. MPCA has 70 percent of the density and 90 percent of the performance of standard cells, and implements customization using the top three metal layers, according to the company. 153 pins are available for I/O. The device is built on UMC's 0.18um process technology, and is packaged in a 308-/388-/484-pin FBGA.

The PC-1 is supported by comprehensive development tools, including the above A320 emulation platform for SoC integration and verification during early development

Faraday says it offers a comprehensive set of software and hardware development tools, including: Linux and Windows CE operating systems, an IDE with compiler, assembler and linker, companion IP drivers, ICE, IA protocols, evaluation boards, and documentation.

According to Faraday's vice president of R&D and marketing, Dr. George Hwang, “There are hundreds of peripheral applications with 100,000 units or less annual volume which require low NRE cost and fast turnaround time. Faraday's PC-1 is the best fit for these markets.”

Price and Availability

Engineering samples of the PC-1 are expected to be available in June 2005. Typical NRE (non-recurring engineering cost) is $144,000, with 25-day turn-around time, according to the company. The chip itself is priced at $13 in 10,000 piece quantities.

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.