Linux-ready MIPS64 SoCs jump to 32 cores

Apr 14, 2009 — by Eric Brown — from the LinuxDevices Archive — 15 views Cavium Networks released a new family of multi-core, MIPS64-based “Octeon” networking system-on-chips (SoCs) with up to 32 cores. The Octeon II Internet Application Processor (IAP) family delivers up to four times the performance of its Octeon Plus processors, plus dozens of application accelerator engines, Cavium says.

Cavium Networks released a new family of multi-core, MIPS64-based “Octeon” networking system-on-chips (SoCs) with up to 32 cores. The Octeon II Internet Application Processor (IAP) family delivers up to four times the performance of its Octeon Plus processors, plus dozens of application accelerator engines, Cavium says.

Like Cavium's previous Octeon Plus family, the Octeon II targets networking, storage, wireless, and control applications. Its range is said to be extended to converged data, voice, and video applications for cloud computing, virtualization, HD video over IP, Web 2.0, and mobile 3G/4G. Other specific applications listed include switches, routers, appliances, WiMAX, LTE, wireless LAN, and unified storage systems and adapters.

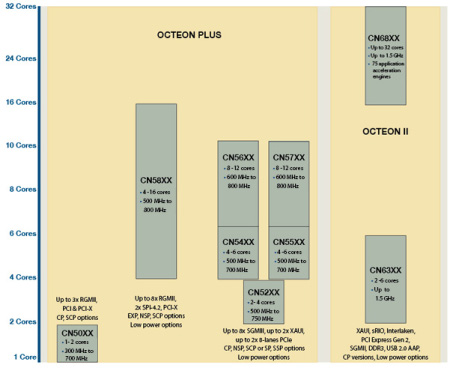

The Octeon II appears to live up to Cavium's claim of being “massively integrated,” as it is said to combine up to 75 application acceleration engines, power optimization components, and features that support virtualization. Unlike the Octeon Plus processors, which topped out at 16 cores with its top-of-the line CN5860, the Octeon II offers versions that combine up to 32 MIPS64 cores. Cavium further claims that the Octeon II offers more than twice the performance per Watt and performance per dollar than the Octeon Plus. (See farther below for more background on Octeon and Octeon Plus processors.)

The initial CN63xx model (pictured at the top of our story), which should start sampling in the fourth quarter, will offer only between two and six cores, but a CN68xx line of Octeon II processors is due next year, ranging from 16 to 32 cores, says Cavium. At some future date, Cavium plans to fill in the gap with the CN66xx (8 to 16 cores) and the CN62xx (one to 4 cores).

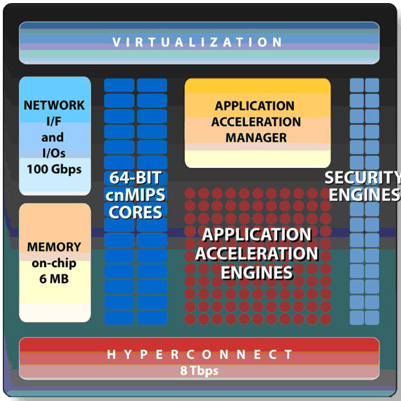

Octeon II architecture

The Octeon II acceleration engines support a variety of QoS and packet processing tasks, as well as networking I/O. The CN63xx models will be offered in Control Plane (CP) and Application Acceleration Processor (AAP) versions. The CP version incorporates general purpose MIPS64 cores and networking hardware acceleration, while the AAP version adds hardware acceleration for security, regular expression, compression, RAID and de-duplication. The engines are controlled by an Application Acceleration Manager, which is said to enable linear scaling of performance across multiple cores. (See spec list below for more engines included in the CN63xx.)

The Octeon II's new “Hyperconnect” crossbar is touted for its low-latency and virtualization features, and provides up to 400Gbps of DDR3 memory bandwidth and up to 100Gbps of network bandwidth. I/O support is said to include gigabit Ethernet, 10 gigabit Ethernet, PCI Express Gen 2, USB 2.0, serial Rapid I/O (sRIO), and the Interlaken internconnect protocol for high-speed packet transfers, says the company.

Octeon Plus and Octeon II families

(Click to enlarge)

The SoC includes an on-chip “Power Optimizer” that helps the processor consume only 2W to 60W, depending on the model, says Cavium. The CN63xx model is said to have a maximum power consumption of 17 Watts, and is available in a low power version that consumes under seven Watts, says Cavium.

Octeon II CN63xx

The initial CN63xx processor is intended for mainstream high-volume applications including enterprise routers, switches, appliances, 3G/4G base stations, and intelligent storage and server adapters, says Cavium. Features are said to include:

- Core and Caches:

- 2, 4, or 6 x superscalar, dual-issue cnMIPS64 R2 cores

- Each with 37KB I-cache, 32KB D-cache

- Up to 1.5GHz performance for up to 9GHz compute cycles

- 2MB of low-latency L2 cache

- Memory — 64-bit DDR3 memory controller with 100Gbps DRAM bandwidth

- Application acceleration engines:

- Deep Packet Inspection HFA (hyper finite automata) engines

- Security acceleration, including AES, RSA, ECC, and SNOW 3G

- TCP/IP packet processing

- Compression/decompression

- Data de-duplication

- RAID processing

- Packet classification

- Quality of Service (QoS)

- Networking and bus interfaces:

- SGMII (Serial Gigabit Media Independent Interface) with IEEE 1588 timestamp

- XAUI

- PCIe Gen2

- sRIO interfaces

A Linux SDK and support from MontaVista and Wind River

The Octeon II Software Development Kit (SDK) is an enhanced version of the existing Octeon SDK, says Cavium. It includes a Linux SMP, GNU Toolchain, and a “Simple Executive” for fast path applications. Other SDK features are said to include performance tools, a simulator, examples, and APIs for hardware acceleration Cavium also offers additional software toolkits and multi-core software architecture and design consulting services.

Previously the Octeon SDKs have been based on SMP Linux 2.6 distributions from MontaVista or Wind River. Today, both companies announced support for the Octeon II family with their Carrier Grade Linux (CGL) 4.0-compliant MontaVista Linux and Wind River Linux 3.0 distributions, respectively.

Octeon and Octeon Plus background

Cavium offers over 30 models of its Octeon and Octeon Plus processors, which are primarily targeted at CGL networking applications. The company announced its Octeon line of processors back in 2005, starting with the four- to 16-core Octeon CN38xx line. Cavium started shipping the CN58xx line of Octeon Plus processors in early 2007, claiming the chips doubled performance while maintaining the same power budget, pin-out, and software compatibility. Since then, it has filled in the Octeon Plus line with additional mid-range models such as the CN52xx.

Octeon Plus CN58xx models are offered in four, eight, 12-, and 16-core versions, with clock speeds ranging from 600MHz to 1GHz, and power consumption ranging from 15 to 40 Watts. The top-of-the-line, 16-core CN5860 integrates hardware engines for TCP offload, compression/decompression, regex, cryptography, and packet queuing and scheduling.

According to Linley Gwennap, principal analyst at The Linley Group, “The OCTEON II architecture is carefully balanced in the number of cores, frequency, hardware acceleration, multicore scheduling, internal interconnects, memory bandwidth and interfaces.”

Ken Klein, President and CEO of Wind River, said, “Working closely together, we are providing the software foundation for customer applications to easily harness the full power of OCTEON II's 32 cores.”

Stated Syed Ali, President and CEO at Cavium Networks, “OCTEON II will fuel the growth of emerging hyper-network applications such as cloud computing, data center virtualization, smart storage, 4G/LTE wireless, HD video over the Internet and multimedia rich Web 2.0 applications.”

Availability

The Octeon II IAP CN63xx processors will sample in Q4 2009, at prices ranging from $60 to $200 in 10K quantities, says Cavium. They will be available in scalable options ranging from two-core to six-core versions running at 800MHz to 1.5GHz, offered in CP and AAP. More information on the Octeon II family may be found here.

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.