Multi-threaded RISC cores released for Linux, Android

Nov 24, 2009 — by Eric Brown — from the LinuxDevices Archive — 24 viewsImagination Technologies is releasing its second-generation 32-bit Meta processor cores for wider availability. The Series2 Meta core IP integrates DSP functions, supports hardware multi-threaded execution, offers hard real-time capabilities, and supports Linux and Android, says Imagination, which also announced a new PowerVR SGX543MP graphics core family.

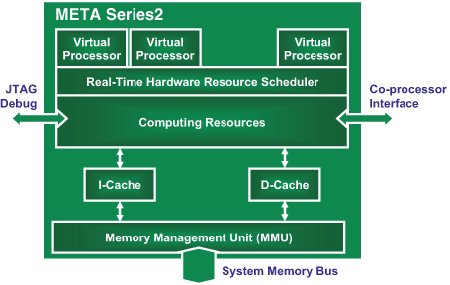

Silicon IP designer Imagination Technologies has long offered its programmable, general-purpose RISC Meta cores, available with Linux support. Featuring an integrated DSP (digital signal processor), the cores provide on-die cache and a memory management unit (MMU), complete with virtual memory support.

In 2005, Imagination announced its first Meta Series2 cores, including the Meta122 CPU, a multi-threaded 32-bit RISC CPU, touted as being able to execute multiple DSP tasks without cross-task interference. The CPU is said to offer latency-immune architecture, as well as deterministic real-time performance.

The Meta122 can be found in Frontier Silicon's Chorus 2 multimedia system-on-chip (SoC), which is in turn incorporated in the new Linux-based Sensia Internet radio (pictured below), developed by Imagination Technologies' "Pure" consumer electronics subsidiary.

Pure's Meta Series2-based Sensia Internet radio

According to Imagination Technologies, the Meta Series2 delivers "exceptionally high processor utilization and tolerance to SoC system latencies while also delivering new levels of real-time response that makes them ideal for SoC applications." The cores support Linux or Android applications processor platforms "with fully coherent caches and MMUs," says Imagination. At the same time, the Meta cores can provide "hard real time" capabilities, which the company defines as being able to respond to an external event in a single clock cycle "including complete context switch."

Imagination Technologies' Meta Series2 block diagram

Imagination currently offers three Meta processor lines:

- Meta HTP SoC Application Processors — Billed as an alternative to traditional multi-processor approaches, the HTP core targets SoCs where high-level operating systems (OSes) are essential for application execution, alongside lower level tasks with demanding real-time constraints and DSP requirements, says Imagination.

- Meta MTP SoC Embedded Processors — Aimed at high speed communications applications that require DSP-intensive algorithms like advanced audio, the MTP line is said to utilize native code execution for maximum performance, and can be combined with Linux or an RTOS (real-time operating system) such as Imagination's MeOS.

- Meta LTP Embedded Controllers — These tiny, single-threaded, 32-bit cores deliver "full compatibility with other Meta processors in a negligible silicon footprint," says the company.

Using Meta's hardware multi-threading capabilities, SoC designers can create multiple virtual processors, thereby consolidating the various processing nodes used throughout the SoC under one consistent processor architecture, says Imagination.

Meta's multi-threading implementation enables the processors to change between hardware contexts on every clock cycle, with up to four threads supported. While a memory request for a Linux application on one thread is being resolved, for example, an audio decoder can progress on another thread while data is progressing though a communications protocol stack on another, and real-time hardware events are serviced on another, claims Imagination.

Meta is the only processor architecture able to support multiple OSes without the need for any virtualization layer, claims Imagination. Meta cores are said to support Linux in both single processor configurations and SMP versions, enabling "software engineers to take advantage of many of the benefits of hardware multi-threading without having to write any special code." Meta also supports its own MeOS RTOS, which it says "is highly suitable for porting other high level open source OS such as Symbian or Android."

Like the Chorus 2 SoC found in the Sensia, SoCs based on the new Meta Series2 cores can also incorporate Imagination's communications core, the Ensigma UCCP IP. The Ensigma enables WiFi, analog and digital TV, mobile TV, and digital and analog radio playback, says the company.

Stated Tony King-Smith, VP marketing, Imagination, "For too long chip designers have stuck to traditional concepts of CPU-based SoC design, which is increasingly not appropriate for the levels of system integration we're now seeing in SoCs. Embedded processors — whether running applications under Linux or highly optimized DSP algorithms — now need to be much more effective in ensuring every clock cycle counts to minimize power and maximize performance."

New PowerVR core to ship by year's end

Imagination Technologies also announced that a new version of its OpenGL ES 2.0 ready PowerVR SGX 2D/3D graphics core will ship by the end of the year. The new SGX543MP core can support SoCs with up to 16 graphics cores in configurations delivering "performance comparable to many desktops, laptops, and games consoles," says the company.

Multiple lead partners have already been working with beta versions of IP for several months, and several SoCs using the cores are already in advanced design, says Imagination. Versions of the core IP will range from the SGXMP2 (two-core) to SGXMP16 (16-core) variants.

The PowerVR SGX543MP family cores are said to enable highly linear scaling of all aspects of GPU performance, including vertex shading, pixel shading, primitive setup, and overall GP-GPU functionality. At 200MHz core frequency, an SGX543MP4 (four cores) can deliver 133 million polygons per second and fill rates in excess of 4Gpixels/sec, and at 400MHz frequency, an SGX543MP8 (eight cores) can deliver 532 million polygons per second and fill rates in excess of 16Gpixels/sec, claims the company.

For years, PowerVR graphics cores have been available in dozens of variants. In the embedded Linux world, they are perhaps most notable for their availability with SoCs based on ARM Cortex-A8 CPU cores, such as the Texas Instruments OMAP family.

Availability

Imagination is now offering all members of the Meta Series2 family of SoC processors for licensing. The company says that "further details of the new IP core family will be announced in the coming months."

More information on Meta Series2 may be found here.

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.