Multicore MIPS64 chips gain virtualization

Jan 21, 2008 — by Eric Brown — from the LinuxDevices Archive — 4 views French embedded virtualization firm Trango Virtual Processors is porting its hypervisor technology to multicore MIPS64 processors from Cavium Networks. The Linux-compatible Trango Hypervisor will be integrated with Cavium's Linux-friendly Octeon line of multi-core processors, with resulting benefits in… throughput and power savings, says Trango.

French embedded virtualization firm Trango Virtual Processors is porting its hypervisor technology to multicore MIPS64 processors from Cavium Networks. The Linux-compatible Trango Hypervisor will be integrated with Cavium's Linux-friendly Octeon line of multi-core processors, with resulting benefits in… throughput and power savings, says Trango.

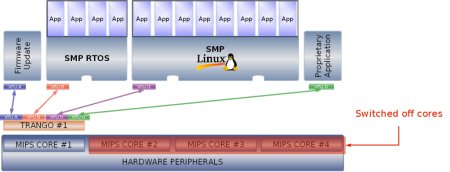

According to Trango, its Hypervisor lets Octeon developers create on-demand virtual processors across the up to 16 MIPS cores available in Octeon processors, which are typically found in carrier grade telecommunications equipment. The virtualization technology will provide Octeon customers with high-availability, application reliability, and user-data security, said Frank Altschuler, Trango's director of marketing, yet the key benefits in a multi-core environment are said to be adaptive resource allocation, I/O virtualization, and power reduction.

Trango Hypervisor in a MIPS multicore environment

(Click to enlarge)

Octeon developers will be able take advantage of many of the features found on Trango's single-core implementation, Altschuler said in an interview, including the ability to easily and safely upgrade firmware in the background or to create a secure domain for running an operating system (OS) without providing [full] access to underlying hardware. Yet, virtualization's big pay-off in the multi-core environment lies in improved throughput and power savings due to dynamic load balancing, he said.

“In a multi-core environment, you typically need to statically assign various processing tasks to the cores,” said Altschuler, “but with virtualization you can instead have dynamic assignments, which improve throughput and provide significant power savings.”

The process is far more complex than simply multiplying the virtualization process times 16, he said. The Trango Hypervisor works closely together with the Octeon's own firmware to dynamically allocate cores and hardware resources to different system functions and features. The technology is said to reallocate processing power between different system functions with “fine granularity” to meet real-time demand. I/O virtualization enables networking OEMs to provide QoS (quality-of-service) for multimedia enabled systems, says Trango, and the Hypervisor works with Octeon's power management capabilities to consolidate processing load to active cores and shut down unnecessary cores.

Cavium Octeon architecture

(Click to enlarge)

Trango's Hypervisor comprises a 20KB microkernel capable of hosting two or more guest OSes per processor core. Because it runs the guest OSes in CPU user mode, rather than protected mode, says Trango, it offers improved security compared to other virtualization products. It ships on ARM, PPC, and MIPS architectures, and will ship this quarter in a version for multi-core ARM11 processors. In Q2 2008, Trango plans to ship a version supporting ARM's new multiprocessor-enabled Cortex A9 processors.

Cavium Octeon network processors ship with MontaVista or Wind River Linux distros. Cavium achieved its first major design win this summer when tier 1 NEP (network equipment provider) Motorola announced its ATCA-9301 blade. Now sold by Emerson Network Power as a result of its recent acquisition of Motorola's Embedded Communications Computing group, each of the blades can be configured with one or two Octeon Plus CN5860 processors, for up to 32 cores per blade. The 900MHz CN5860 processor also integrates hardware engines for TCP offload, compression/decompression, regex, cryptography, and packet queuing and scheduling.

Availability

The integrated Trango Hypervisor product will be available along with an Eclipse-based tools suite for Octeon customers starting in Q1 2008, says Trango.

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.