SoC for DVRs combines 1GHz Cortex-A8 with DSP

Mar 23, 2010 — by LinuxDevices Staff — from the LinuxDevices Archive — 15 viewsTexas Instruments (TI) announced a high-end SoC for DVRs and video communications systems that combines a 1GHz Cortex-A8 with a C64x+ DSP. The TMS320DM8168 has four times the performance of its predecessor, handling up to three channels of 1080p video or 16 D1 streams, the company says.

TI's DaVinci family of video-oriented SoCs (system-on-chips) includes multiple devices, some sporting both ARM9 application processors and DSPs (digital signal processors), some with only ARM9 processors, and some that are only DSPs. Examples with ARM9 CPUs and DSPs on board include TI's first DaVinci chips, the TMS320DM6443 and TMS320DM6446, announced back in 2005, as well as the later TMS320DM6467. DaVinci processors equipped with only ARM9 CPUs include the TMS320DM335, TMS320DM355, and last year's TMS320DM365.

According to TI, its fastest DaVinci SoC to date has been the TMS320DM6467T, released last November. The chipmaker describes this part as running at 1GHz because of the speed of its C64x+ DSP core, but its ARM9 core clocks at 500MHz.

TI's new, high-end TMS320DM8168 (hereinafter, just "DM8168") moves up to 1GHz throughout, combining the C64x+ DSP core with a 1GHz ARM Cortex-A8 core. (This combo is new to the DaVinci line, but not to TI as a whole — the OMAP3525 and OMAP3530, for example, also use the C64X+ with a Cortex-A8 core.)

The chipmaker says the DM8168 has four times the video compression performance of the TMS320DM6467T, plus increased multi-channel density and support for higher resolutions. Offering "an order of magnitude increase in HD video pre- and post-processing," the SoC can handle three channels of 1080p at 60fps, according to the company.

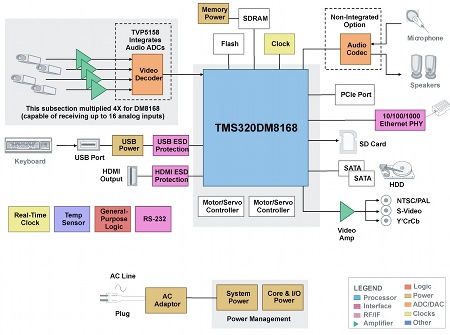

Block diagram of a DM8168-based DVR

(Click to enlarge)

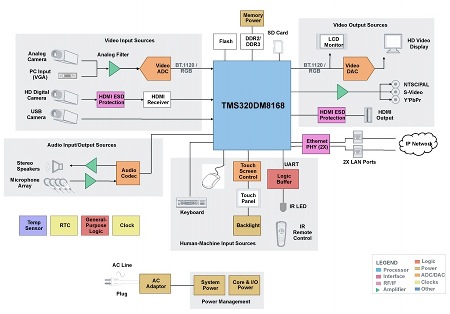

Block diagram of a DM8168-based video communications system

(Click to enlarge)

TI has not released a block diagram of the DM8168 itself, but it did release the above diagrams of the SoC being used at the heart of a DVR (digital video recorder) and a video communications system. The SoC includes multiple interfaces including gigabit Ethernet, PCI Express, SATA 2, DDR2, DDR3, USB 2.0, MMC/SD, and HDMI, the company says.

According to TI, the DM8168 also includes a glueless interface to four separately available TVP5158 video decoders. With the aid of these parts, the SoC can "seamlessly" capture up to 16D1 (SDTV) channels, with automatic noise reduction and contrast control, the company says.

Availability

TI says the DM8168, claimed to replace more than ten discrete components and to reduce BOM costs by 50 percent, will begin sampling during the second quarter of this year.

To accelerate design cycles, TI adds, it will offer video security and video communications evaluation modules (EVMs). Each EVM will come complete with a reference hardware board, software, tools and demonstration applications, allowing for evaluation of video processing capabilities and performance, as well as immediate application development. Developers will also have access to a complete EVM support package, including a full software framework and design suite that "abstracts the internal complexity of the DM8168 video SoC," the company says.

Operating system support and pricing were not detailed, but previous DaVinci processors have supported Linux and Windows CE. Previous DaVinci chips have also been supported on Linux by Timesys' LinuxLink development framework. More information on the DM8168 may eventually be found on TI's website, here.

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.