ARM aims son of Thumb at uCs, ASSPs, SoCs

Oct 19, 2004 — by LinuxDevices Staff — from the LinuxDevices Archive — 22 views[Updated Nov. 1, 2004] — ARM Ltd. unveiled a new 16/32-bit CPU instruction set technology, called “Thumb-2,” at the Fall Processor Forum on October 19. Thumb-2 aims to bring uniformity to a broad swath of processors, from ultra-low-cost microcontroller (uC) level chips to high-end “application specific standard processors” (ASSPs) and system-on-chip (SoC) processors.

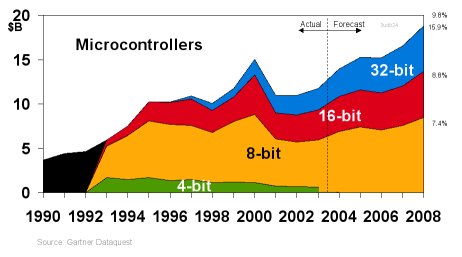

For the first time, ARM says, a single software instruction set architecture (ISA) will be usable in devices as disparate as wrist-watches, mobile phones, MP3 players, telecommunications infrastructure, and supercomputers — essentially serving the entire 8-, 16- and 32-bit microcontroller market, valued by Gartner at over $10B in 2003 and growing fast (see graph).

Growth of the 32-bit microcontroller market

(Click above image for larger version)

Thumb-2 as basis of Cortex

The new Thumb-2 ISA forms the technology basis of a new family of CPU cores being developed by ARM, which fall under the “Cortex” monicker, also announced on October 19.

The first member of ARM's Cortex processor family will be the low-end M3 (in the Cortex M series) which specifically targets cost-sensitive applications previously served primarily by 8-bit microcontroller chips. Higher-end Cortex processor cores will follow, targeting mid-range real-time-control processors (the Cortex R series) and performance-driven application processors which run complex operating systems and software applications (the Cortex A series).

But, whereas the Cortex-M3 and other cores in the Cortex M series will only include the Thumb-2 ISA, the Cortex A and R series processor cores will combine the Thumb-2 ISA along with ARM's recently announced Neon DSP media and signal processing instruction set extensions, as well as including the full 32-bit ARM ISA enabling backwards compatibility with today's high-end ARM ISA based cores such as the ARM9, ARM10, and ARM11.

Cortex family roadmap

ARM's product roadmap for its Cortex family calls for the Thumb-2 instruction set to appear in a surprisingly broad range of processors, a versatility not unlike that of Linux itself. The Cortex family processor cores, rolled out over the next three years, will include the following three classes of processors spanning clock rates ranging from 1MHz to 1GHz+, ARM says:

- A-series — high-end application processors focused on the execution of complex OSes and applications

- R-series — mid-range embedded processors targeting the traditional real-time embedded control market

- M-series — low-end processors focused on highly cost-sensitive, deterministic, interrupt-driven applications and replacing one or more 8- or 16-bit microcontrollers

About the Thumb-2 ISA

ARM's new Thumb-2 instruction set architecture (ISA) is a successor to the well-known and popular Thumb ISA, which is included in today's 32-bit ARM cores that have a “T” designator (e.g. the popular ARM920T). The original Thumb ISA implements a subset of 32-bit ARM instructions re-coded in 16-bit format, and targets 8- and 16-bit microcontroller-level applications.

According to ARM CTO Mike Muller, Thumb-2 is a blended 16/32-bit instruction set that runs all of the old 16-bit Thumb instructions, but adds many instructions from the 32-bit ARM ISA. And, as a result of careful design, the Thumb-2 ISA produces an excellent compromise between compact code size (a strength of the Thumb ISA) along with good performance (a strength of the ARM ISA), Miller says. Specifically, the Thumb-2 ISA is said to use 26 percent less memory than pure 32-bit ARM ISA code, while at the same offering 25 percent greater performance than the old Thumb ISA's pure 16-bit code. Consequently, in many applications developers will no longer need to worry about selecting between smaller code size (by specifying Thumb ISA instructions) and higher performance (by specifying ARM ISA instructions) — instead, Thumb-2 will provide the best of both worlds, according to Muller.

Moreover, when the 16/32-bit Thumb-2 and 32-bit ARM ISAs are combined in a single processor — as in the A and R series Cortex processors — applications will be able to switch more efficiently between the two ISAs, due to elimination of context-switch overhead penalties, according to ARM product manager Haydn Povey.

The Cortex-M3 processor

The first Cortex processor to see the light of day will be the M3, which only includes the new 16/32-bit Thumb-2 ISA instructions, and implements the smallest and lowest-power core possible, enabling it to deliver “32-bit processing at 8-bit microcontroller prices,” ARM says.

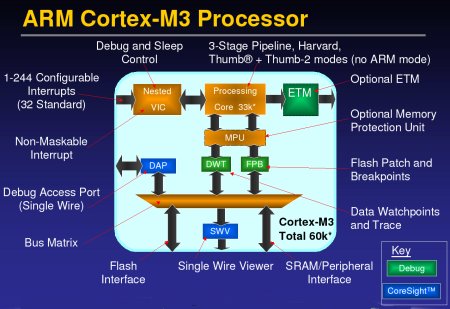

Cortex-M3 Processor function diagram

(Click above image for larger version)

As indicated in the block diagram, the M3 provides the option of a memory protection unit (MPU), though not of a memory management unit (MMU). Unlike an MMU, the optional MPU cannot translate addresses, and therefore cannot support “complex” OSes, such as standard Linux or Windows CE. However, Muller says, the M3 will support uClinux (now a compile-time option of Linux), since uClinux does not require the presence of an MMU.

M3 availability

The Cortex-M3 processor core is available for licensing now, ARM says. Simulation models will be available early next year, and first silicon samples are expected by mid-year. Development tools and synthesizable RTL are expected by Q3, 2005, and ready-to-use reference boards should begin arriving by the begining of 2006.

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.