Via comes to the quad-core CPU party

May 12, 2011 — by LinuxDevices Staff — from the LinuxDevices Archive — viewsVia announced a quad-core version of its Nano processor, boasting a TDP of just 27.5 Watts. Simply named the “QuadCore,” the CPU features adaptive overclocking, 4MB of L2 cache, the PadLock cryptography engine, and pin-to-pin compatibility with earlier Via CPUs, the company says.

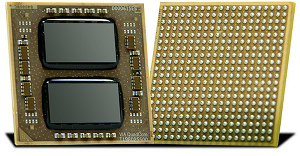

According to Via, its 40nm-fabbed QuadCore processor (right) combines four "Isaiah" cores (see later) on two 11 x 6mm dies, integrated into a 21 x 21mm package. Conveniently, it's pin-to-pin compatible with earlier Via CPUs such as the dual-core Nano X2, the single-core Nano, the C7, the C7M, and the Eden, according to the company. (Though Via didn't say, the QuadCore apparently will work with previously released chipsets, too, such as the VN1000 and VX900.)

According to Via, its 40nm-fabbed QuadCore processor (right) combines four "Isaiah" cores (see later) on two 11 x 6mm dies, integrated into a 21 x 21mm package. Conveniently, it's pin-to-pin compatible with earlier Via CPUs such as the dual-core Nano X2, the single-core Nano, the C7, the C7M, and the Eden, according to the company. (Though Via didn't say, the QuadCore apparently will work with previously released chipsets, too, such as the VN1000 and VX900.)

We've complained following recent product launches — like the one earlier this month for the seven-year-available Nano X2 E-Series — that Via doesn't provide details of its processors' power consumption. With the QuadCore, the company has corrected that omission, touting a TDP of just 27.5 Watts.

The QuadCore is "21 percent more energy efficient than the nearest competitor," Via claims. Performance isn't quantified, but the company says the "1.2+ GHz" CPU "delivers awesome multi-threaded performance across the board for multi-tasking, multimedia playback, productivity and Internet browsing."

Via's Nano X2 (left) and new QuadCore (middle)

(Click to enlarge)

According to Via, the QuadCore's four CPU cores enhance performance with applications that have been optimized for multiple threads. Like the Nano X2s and the revised single-core Nanos that debuted in November 2009, the processor supports both Via's VT virtualization technology and Intel's SSE4 instruction set extensions. (Previous Nanos supported only SSE3, just like Intel's own Atom.)

Via's PadLock security engine is once again featured, and is now promoted as adding the "world's fastest AES [Advanced Encryption Standard] encryption." Offered at least since the 2003 introduction of the Eden-N, PadLock imposes significantly less overhead than software-based encryption, according to the chipmaker.

Epan Wu, head of processor platforms for Via, stated, "As a result of the rapid proliferation of high definition multimedia content and increasingly demanding multithreaded applications, a four-core processor is the new baseline for today's mainstream PC user. The Via QuadCore processor meets that need with the industry's most power efficient architecture."

Background on the Isaiah core

Via's Esther (used in the C7 and Eden) and Isaiah (used in the Nano) microarchitectures were designed by the company's CenTaur chip unit, headed up by Glenn Henry, a former IBM engineering fellow. Whereas Esther — like Intel's Atom — uses in-order execution, for the lowest power and size requirements, Isaiah uses out-of-order execution, similar to Intel's Core Duo architecture.

Isaiah added compatibility with the 64-bit architectures already used by Intel and AMD, plus SSE3 media processing instructions. Another touted Isaiah feature was a reworked floating point unit.

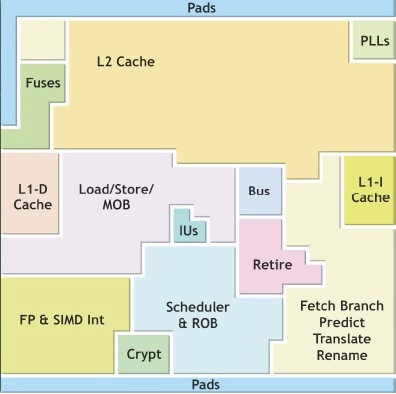

A block diagram of the Via Nano

The Nano processors were the first 64-bit, superscalar, speculative out-of-order processors in Via's x86 platform portfolio. They can decode three full x86 instructions per clock, generate three fused (internal machine instructions) micro-ops per clock, issue (speculatively and out-of-order) seven execution micro-ops per clock to seven execution ports, and retire three fused microops per clock.

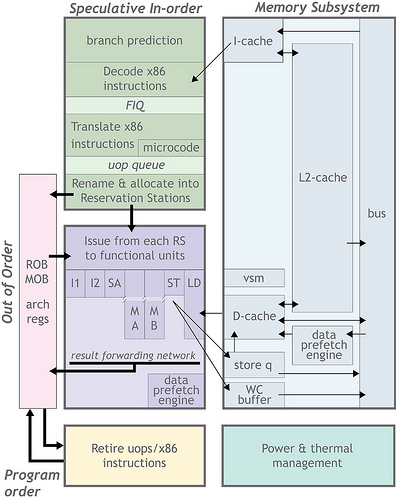

A conceptual diagram of Via's Nano architecture

As the above conceptual picture illustrates, the Nano processors include pipelines that fetch x86 instruction bytes and translate them into micro-ops. The x86 instructions and micro-ops proceed in program order down the top left ("in-order") portion of the pipeline.

The "speculative" label refers to the fact that the processor may not be actually fetching the correct program instructions (in cases of a branch misprediction, for example). "Out-of-order" issue and execution happens when the pipeline components take the translated micro-ops and issue them to the appropriate execution units. This happens whenever inputs are available, not necessarily in program order.

A "completely new algorithm for floating-point results in the lowest floating-point add latency of any x86 processor," the company said in a 2008 whitepaper about the Isaiah architecture. In addition, the integer data path for SIMD integer (SSEx) instructions is 128-bits wide, and almost all SSEx instructions (including all shuffles) execute in only one clock.

Availability

According to Via, the QuadCore processors will be on display at the Via booth at Computex (Taipei International Convention Center, Room 201D) from May 31 to June 4, and will begin volume shipments during the third quarter. Further information may be found on the QuadCore product page.

Jonathan Angel can be followed at www.twitter.com/gadgetsense.

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.