GbE “switch-on-a-chip” runs eCos

Dec 17, 2008 — by Eric Brown — from the LinuxDevices Archive — 15 viewsVitesse Semiconductor announced a second generation of its ARM9-based “switch-on-a-chip” that runs the open source eCos RTOS (real-time operating system). The 24-port SparX-II-24 and 16-port SparX-II-16 target networking applications requiring “content-aware” security, failover protection, and quality-of-service (QoS) filtering, says the company.

Vitesse says the SparX-II chips offer wire-speed, deep packet inspection for security and other heavy packet inspection applications, says Vitesse. Target applications include web-managed, or SNMP-managed standalone switches, including mbedded switch backplane applications, modular computer servers, and DSLAMs (DSL access multiplexers). Additional applications for the 24-port version include VoIP, IPTV, WLAN, and “triple-play” (voice, data, video) enabled switches, says the company.

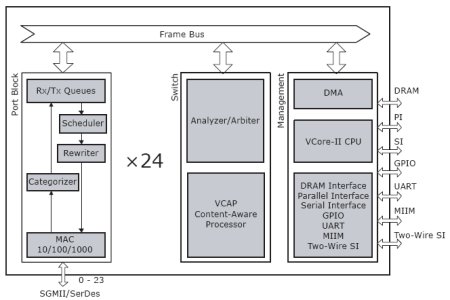

The SparX-II chipset is built around the company's ARM926EJ-S-based “VCore-II” CPU. It also includes Vitesse's VCAP co-processor core, which seems to be derived from Cisco's Ternary Content-Addressable Memory (TCAM) technology. The SparX-II-24 boasts a 1184KB on-chip frame buffer and 24 gigabit Ethernet ports, while the SparX-II-16 offers an 800KB frame buffer and 16 ports. Otherwise, the two chipsets appear to be identical.

SparX-II-24 block diagram

(Click to enlarge)

Vitesse says the VCAP co-processor can deliver “wide” data searches in short, fixed time periods, supporting in- or out-bound wire-speed packet inspection, frame filtering, rate limitation, snooping, redirect, mirroring, and accounting functions, says the company. The processor is said to provide “content awareness” for protocols including ARP, IPv4, IPv6, and UDP/TCP. Redundancy switching times, meanwhile, are claimed to be “significantly below” the 50ms SONET telecom specification.

Features listed for the SparX-II chipsets include:

- VCore-II ARM926EJ-S CPU (clock not specified, but the core is typically clocked to 400MHz)

- VCAP processor for inbound and outbound wire-speed packet inspection

- 1184KB on-chip frame buffer (800KB on SparX-II-16)

- 24 x 10/100/1000 Mbps SGMII/SerDes Ethernet interfaces (16 x ports on SparX-II-16)

- 8KB MAC addresses

- 4KB VLANs (IEEE802.1Q)

- 8KB IPv4/IPv6 multicast group support

- DSCP remarking for both IPv4 and IPv6 frames

- QoS control lists for programmable QoS classification

- Traffic shapers for rate limitation of ingress and egress traffic

- Metro Ethernet Forum-specified (MEF) Carrier Ethernet

- Vitesse Copper PHY voltage-mode line driver and power management technology

- Supports most L2 switching protocols, including MSTP, LACP, LLDP, and IGMP snooping

- Third-party software support for Power over Ethernet and Synchronous Ethernet

- eCos real-time operating system (RTOS)

eCos offers a smaller footprint than Linux, making it more suitable for a wide range of lower-powered embedded systems. Developed and maintained for years by Red Hat via its Cygnus acquisition, eCos has been primarily maintained by eCosCentric since all its patents were unified under the Free Software Foundation (FSF) in 2004.

Stated Martin Olsen, product marketing manager for Vitesse, “SparX-II delivers against high security and advanced prioritization challenges so that our Carrier Network, backplane, and SME customers can meet design challenges.”

Availability

The SparX-II-16 (also called the VSC7401) and the SparX-II-24 (VSC7405) are in full production, says Vitesse. More information on the SparX-II-16 may be found here, and more on the SparX-II-24 should be here.

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.