Via’s Nano gets dual cores

Jan 4, 2011 — by LinuxDevices Staff — from the LinuxDevices Archive — 3 viewsVia Technologies says it is now sampling a dual-core version of its 64-bit Nano processor. The Nano X2 provides out-of-order execution, VT CPU virtualization support, SSE4 instruction set extensions, and PadLock hardware security features, the company says.

According to Via, its new Nano X2 (right) comes in the same 21 x 21mm package as previous Nanos, with which it's pin-to-pin compatible. But, instead of being fabbed using a 65nm process, it moves to 40nm, making room for dual "Isaiah" cores.

According to Via, its new Nano X2 (right) comes in the same 21 x 21mm package as previous Nanos, with which it's pin-to-pin compatible. But, instead of being fabbed using a 65nm process, it moves to 40nm, making room for dual "Isaiah" cores.

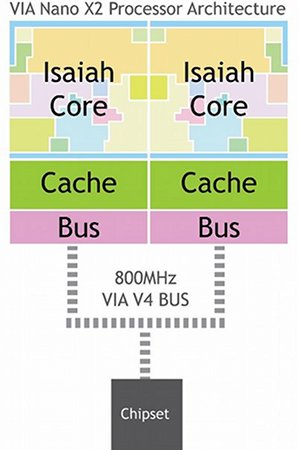

Via says the dual cores (below) essentially double up performance with applications that have been optimized for multiple threads. Otherwise, the Nano X2 is much the same as the revised single-core Nanos that debuted in November 2009: Like these, it supports Intel's SSE4 instruction set extensions, plus Via's VT virtualization technology. (Previous Nanos supported only SSE3, just like Intel's own Atom.)

The Nano X2's dual Isaiah cores

(Click to enlarge)

A continuing point of pride for Via is its PadLock security engine, once again featured on the Nano X2. Offered at least since the 2003 introduction of the Eden-N, PadLock offers hardware-based Advanced Encryption Standard (AES) functionality, and imposes significantly less overhead than software-based encryption, according to the company.

According to Via, the Nano X2 is not only pin-compatible with earlier Nanos, but also with the earlier C7, C7M, and Eden CPUs. The processor is further said to work with all of Via's previously released chipsets, including the VN1000 introduced in December 2009 and the VX900 from March 2010.

Via didn't provide information about the Nano X2's TDP or idle power consumption, but does say the processor offers its increased performance "without consuming more power." The table below summarizes the power consumption data the chipmaker has made available for its previous Nano offerings.

| Name | Speed | Idle power | Maximum power (TDP max) |

| L3100 | 2.0GHz | 500mW | n/s |

| L3050 | 1.8GHz | 500mW | n/s |

| U3200 | 1.4GHz | 100mW | n/s |

| U3100 | 1.3+GHz | 100mW | n/s |

| U3300 | 1.2GHz | 100mW | n/s |

| U3500 | 1.0GHz | 100mW | n/s |

| U3400 | 800MHz | 100mW | n/s |

| L2100 | 1.8GHz | 500mW | 25.5W |

| L2200 | 1.6GHz | 100mW | 17W |

| U2400 | 1.3GHz | 100mW | 8W |

| U2500 | 1.2GHz | 100mW | 6.8W |

| U2300 | 1.0GHz | 100mW | 5W |

Via's previous Nanos

(models highlighted in red debuted in November 2009; U3400, in green, debuted in March 2010)

Richard Brown, vice president of international marketing for Via, stated, "The Via Nano X2 processor arrives at a time when software architectures are now optimized for multi-thread computing. Improvements in semi-conductor fabrication means we can now double the number of processor cores while maintaining the same low energy consumption levels that our customers are used to."

Background on the Isaiah core

Via's Esther (used in the C7 and Eden) and Isaiah (used in the Nano) microarchitectures were designed by the company's CenTaur chip unit, headed up by Glenn Henry, a former IBM engineering fellow. Whereas Esther — like Intel's Atom — uses in-order execution, for the lowest power and size requirements, Isaiah uses out-of-order execution, similar to Intel's Core Duo architecture.

Isaiah added compatibility with the 64-bit architectures already used by Intel and AMD, plus SSE3 media processing instructions. Another touted Isaiah feature was a reworked floating point unit.

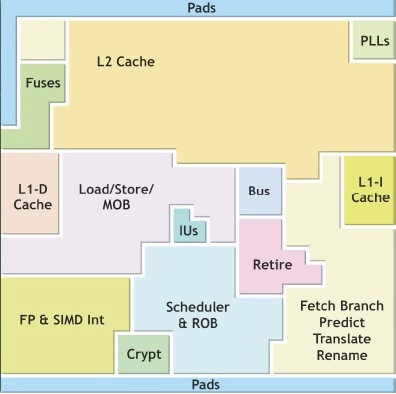

A block diagram of the Via Nano

The Nano processors were the first 64-bit, superscalar, speculative out-of-order processors in Via's x86 platform portfolio, according to the company. They can decode three full x86 instructions per clock, generate three fused (internal machine instructions) micro-ops per clock, issue (speculatively and out-of-order) seven execution micro-ops per clock to seven execution ports, and retire three fused microops per clock.

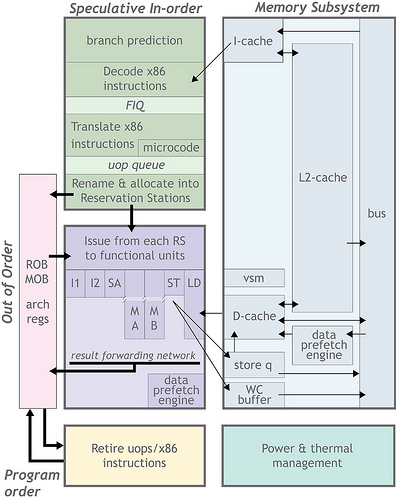

A conceptual diagram of Via's Nano architecture

As the above conceptual picture illustrates, the Nano processors include pipelines that fetch x86 instruction bytes and translate them into micro-ops. The x86 instructions and micro-ops proceed in program order down the top left ("in-order") portion of the pipeline.

The "speculative" label refers to the fact that the processor may not be actually fetching the correct program instructions (in cases of a branch misprediction, for example). "Out-of-order" issue and execution happens when the pipeline components take the translated micro-ops and issue them to the appropriate execution units. This happens whenever inputs are available, not necessarily in program order.

A "completely new algorithm for floating-point results in the lowest floating-point add latency of any x86 processor," the company said in a 2008 whitepaper about the Isaiah architecture. In addition, the integer data path for SIMD integer (SSEx) instructions is 128-bits wide, and almost all SSEx instructions (including all shuffles) execute in only one clock.

Availability

According to Via, its Nano X2 is sampling now, and devices based on it should become available during the first quarter. Further information may be found on the Nano X2 product page.

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.