ARM unveils multi-processor core with Linux SMP support

May 17, 2004 — by LinuxDevices Staff — from the LinuxDevices Archive — 35 viewsARM Ltd. will unveil a unique multi-processor core technology, capable of up to 4-way cache coherent symmetric multi-processing (SMP) running Linux, this week at the Embedded Processor Forum in San Jose, Calif. The “synthesizable multiprocessor” core — a first for ARM — is the result of a partnership with NEC Electronics announced… last October, and is based on ARM's ARMv6 architecture.

ARM says its new “MPCore” multiprocessor core can be configured to contain between one and four processors delivering up to 2600 Dhrystone MIPS of aggregate performance, based on clock rates between 335 and 550 MHz. Additionally, the MPCore core implements ARM's “Adaptive Shutdown” and “Intelligent Energy Manager” power management technologies, which enable power consumption to be reduced by up to 85 percent, according to ARM.

ARM's processor cores are used by numerous chip manufacturers to develop specialized system-on-chip processors. For example, Intel uses ARM cores in its popular XScale processors, as does TI in its OMAP chips.

MPCore targets a broad range of convergence applications requiring high performance and low power consumption, and where multiple tasks can execute semi-independently on separate processor, according to ARM. Examples include consumer entertainment and convergence devices in the home and car, ARM says, such as a set-top box recording several TV channels while sharing home movies across the Internet, and an in-car navigation system delivering simultaneous back-seat video gaming.

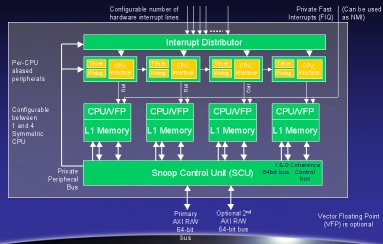

MPCore architecture

(Click above image to enlarge)

The up-to-four processor cores contained within an MPCore multiprocessor can individually be configured for either SMP or AMP (asymmetric multi-processing) operation. So, for example, an application could take advantage of three cores in an SMP arrangement, along with one core used in AMP mode. The choice — SMP or AMP — is configured by setting a bit in a register for each CPU, under software control.

“Multi-processing can give system designers very high processing performance combined with low-power consumption,” explained ARM chief technology officer Mike Muller. “Through our partnership with NEC Electronics we have developed the ground breaking MPCore multiprocessor which delivers the benefits of scalable multi-processing in a configurable and easy to use implementation. Our commitment to producing innovative IP enables our Partners to produce the most advanced digital products, and enrich the end-user experience, in the consumer electronics and networking markets. These are areas where we are seeing considerable growth in the deployment of the ARM architecture.”

Affinity for embedded Linux

Currently, ARM processors — which include Intel's XScale processors — appear to be the most popular processor architectures for new embedded Linux based designs. LinuxDevices.com's recently concluded annual market survey found ARM processor architectures surpassing x86 architecture for new designs, for the first time.

The MPCore multiprocessor will be supported on a broad range of operating system platforms, according to ARM. The first supported OSes are embedded Linux, from MontaVista Software, and Nucleus PLUS RTOS, from Mentor Graphics.

MontaVista will support MPCore's power management technologies using the dynamic power management capabilities built into its Consumer Electronics Edition embedded Linux OS and toolkit. Additionally, Linux natively supports symmetric multiprocessing.

An evaluation system for the MPCore multiprocessor with a Linux 2.6 kernel based operating system and development tools is available today, supporting early software development for MPCore multiprocessor designs, according to ARM.

MPCore evaluation platform hardware

(Click above image to enlarge)

More details

According to ARM, its new MPCore multiprocessor supports ARM's ARMv6 architecture, with SIMD multimedia extensions and Jazelle Java acceleration. The MPCore multiprocessor implements between one and four processors with cache coherency using a modified MESI protocol. It also features configurable level 1 caches, 64-bit AMBA AXI interfaces, vector floating-point coprocessors and programmable interrupt distribution.

The processor supports Adaptive Shutdown of unused processors to give dynamic power consumption as low as 0.57mW/MHz from a generic 130nm process excluding cache. The ARM Intelligent Energy Manager technology can further reduce consumption by dynamically predicting the required performance and lowering the voltage and frequency. The MPCore multiprocessor enables system designers to view the core as a single “uniprocessor”, simplifying development and reducing time-to-market, according to ARM.

Availability

ARM's new MPCore multiprocessor core is available for licensing immediately. First silicon of MPCore-based chips is expected during the second quarter of 2005.

“It's real and people are writing software for it,” an ARM spokesperson said.

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.