Massively multicore SoCs run Linux

Sep 22, 2008 — by Eric Brown — from the LinuxDevices Archive — 9 viewsTilera announced a second generation of its scalable, 64-core Tile64 family of SoCs (system-on-chips). The TilePro family, which includes the 64-core TilePro64 and 36-core TilePro36, doubles cache size and improves cache management, while also benefitting from upgraded Eclipse-based Linux development tools, says the company.

Announced in August 2007, the original Tile64 SoC is fabbed on 90nm process technology at TMSC. It includes 64 cores, each clocked at between 600MHz and 900MHz, and each containing its own L1 and L2 cache. It targets network and video devices that require significant application processing. Examples include surveillance systems, videoconferencing, and firewalls with deep packet inspection. Tilera boasts of having some 45 customers for the processor.

The new TilePro family is said to improve the performance of “highly threaded and shared-memory applications” through a technology Tilera calls Dynamic Distributed Cache (DDC). The feature acts as an on-chip communication network dedicated to cache management, and enables the processors to double both the L1 cache size and L2 cache associativity, says the company.

Tilera claims that TilePro64 performance is double that of Tile64 in networking applications such as Snort and nProbe, while offering “35x better performance-per-Watt over the Quad-Core Xeon.” The TilePro processors have also gained new instruction set extensions for audio and video. The extensions are touted as delivering up to twice the multimedia signal processing performance, compored to the Tile64.

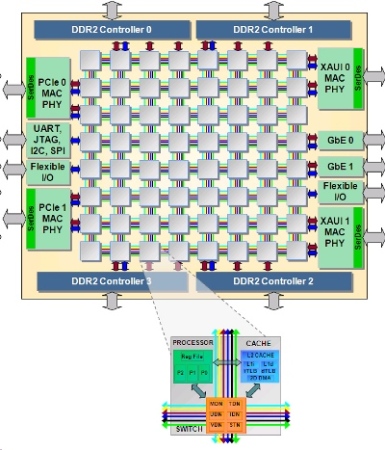

TilePro64 block diagram

The TilePro64 is said to integrate 64 cores, four 800MHz DDR2 memory controllers, and an array of high speed I/O and PCI Express interfaces. The SoC can encode 10 streams of 1080p H.264 video (baseline profile), and execute over 20Gbps of pattern matching in networking applications, claims Tilera.

New TilePro36

Tilera's first 36-core processor, the TilePro36, is aimed at mid-range (1-5Gbps) networking and security applications, videoconferencing endpoints, and midrange multimedia applications, says the company. It is said to offer three DDR2 memory controllers and a “complementary” set of high speed I/O interfaces. Touted functionality includes the ability to deliver 5Gbps of Snort intrusion prevention processing, and three streams of H.264 1080p video encode.

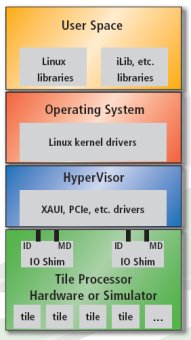

MDE architecture (Click to enlarge) |

Like the Tile64, the TilePro SoCs are based on a proprietary VLIW (very long instruction word) architecture, on which a MIPS-like RISC architecture is implemented in microcode. A hypervisor enables each core to run its own instance of Linux, or alternatively the whole chip can run Tilera's 64-way SMP (symmetrical multiprocessing) Linux implementation. An “iMesh” switching interconnect, developed by Tilera's founder, MIT professor and serial entrepreneur Dr. Anant Agarwal, is said to eliminate the centralized bus intersection that limited scalability in previous multicore designs.

Specific performance features for the TilePro64 include:

- 8 x 8 grid general purpose processor cores (tiles)

- 32-bit VLIW processors with 64-bit instruction bundle

- Three-deep pipeline with up to 3 instructions per cycle

- 5.6MB of on-chip cache

- Up to 443 billion operations per second (BOPS)

- 37Tbps of on-chip mesh interconnect enables linear application scaling

- 200Gbps memory bandwidth with four 64bit DDR2 controllers

The TilePro SoCs are supported by the company's Linux-based development kit, called the Multicore Development Environment (MDE). The Eclipse-based integrated development environment (IDE) offers a runtime environment based on an SMP Linux 2.6 kernel.

Tilera has upgraded MDE to version 2.0 in order to support the TilePro models. MDE 2.0 also offers a new “zero overhead Linux” option that provides “the timing predictability of a stripped-down task scheduler,” says the company. The new version also supports a “bare-metal programming environment with a thin services layer for signal processing and data plane applications,” says Tilera.

Tilera's 10GbE Tile64 PCIExpress card (Click for details) |

In conjunction with its original MDE announcement in April, Tilera introduced a dual 10GbE PCIExpress card based on the Tile64 (pictured at right). Tilera did not reveal whether it would produce new cards based on the TilePro SoCs.

Stated Omid Tahernia, Tilera's president and CEO, “The TILEPro family delivers on our promise of scalability by giving our customers a software and pin-compatible part for high to mid-range applications.”

Stated Nathan Brookwood, Research Fellow at Insight 64, “The new TILEPro64 delivers twice the performance of the earlier TILE64, with only nominal increase in power, while the TILEPro36 comes in at a lower cost for price-sensitive applications. All three versions drop into the same sockets and run the same software-compatible applications.”

Availability

The TilePro64 will be sampling to qualified customers in October, and the TilePro36 will sample in Q4, 2008, says Tilera. More information may be found here.

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.