MIPS-like 32-core SoC runs Linux

Dec 16, 2008 — by Eric Brown — from the LinuxDevices Archive — 1 views Tilera is shipping a 36-core version of its 64-core Tile64 SoC (system-on-chip). Aimed at graphics-intensive embedded applications and networking devices, the TilePro36 clocks from 600MHz to 900MHz, consumes 9-13 Watts (typical), and runs Linux on each, some, or all cores.

Tilera is shipping a 36-core version of its 64-core Tile64 SoC (system-on-chip). Aimed at graphics-intensive embedded applications and networking devices, the TilePro36 clocks from 600MHz to 900MHz, consumes 9-13 Watts (typical), and runs Linux on each, some, or all cores.

The Tile SoCs are based on a proprietary VLIW (very long instruction word) architecture, on which a MIPS-like RISC architecture is implemented in microcode. A hypervisor enables each core to run its own instance of Linux — or other OSes, once they become available. Alternatively, the whole chip can run Tilera's SMP (symmetrical multiprocessing) Linux implementation.

Tilera first announced the TilePro36 in September, concurrently with a 64-way TilePro model. The chips are fabbed on 90nm process technology at TMSC.

The TilePro36 targets mid-range (1-5Gbps) networking and security applications, videoconferencing endpoints, and midrange multimedia applications, says the company. Touted functionality includes the ability to deliver 5Gbps of Snort intrusion prevention processing, three streams of H.264 1080p video encode, and five channels of wireless OFDM processing.

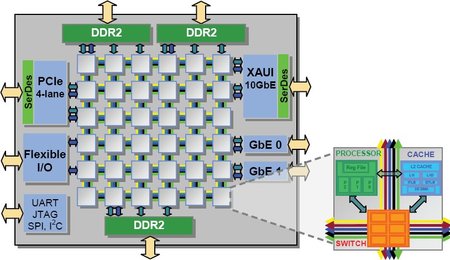

TilePro36 block diagram

(Click to enlarge)

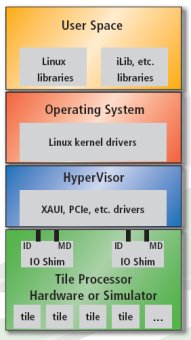

MDE architecture (Click to enlarge) |

The TilePro36 offers three DDR2 memory controllers and a “complementary” set of high speed I/O interfaces. Other touted specs include:

- 36 processor cores, each with integrated L1 and L2 cache

- 3.2MB on-chip cache

- 3 x 72-bit DDR2 memory interfaces (selectable ECC)

- 2 x gigabit Ethernet interfaces

- 10Gbps XAUI Ethernet interface

- 4-lane PCI Express interface

Developer kit

The TilePro SoCs are supported by the company's Linux development kit, called the Multicore Development Environment (MDE) (see diagram at right). The Eclipse-based kit includes an SMP Linux 2.6 kernel, toolchains, and several tools aimed at easing parallel programming. Specifically, these include some profiling tools presumably aimed at helping to identify which parts of an application to parallelize, and an “iLib” parallel programming library aimed at making inter-core communications more efficient by abstracting process management, and providing “socket-like” streaming channels and message passing mechanisms.

Tilexpress64 (Click to enlarge) |

A TilexpressPro-36 PCIe developer board is available for the SoC, says Tilera, but it did not provide further information. The company has, however, posted details on the TilexpressPro-64 PCIe (pictured at left), which incorporates the TilePro64 SoC, and offers an L2-L3 Ethernet switch, six to 12 gigabit Ethernet ports, and an optional mezzanine expansion board connector.

Stated Omid Tahernia, Tilera's president and CEO, “Our customers across market segments look for their high-end solutions to scale down to the mid-range while preserving their software investment. The pin-compatible TILEPro36 fulfills this need.”

According to Tilera, more than 45 customers are using its older 64-core Tile64 SoC, which was announced in August 2007.

Availability

The TilePro36 processor is now sampling along with the TilexpressPro-36 PCIe developer platform, says Tilera. More information should be available here. For more on the TilePro technology, see our earlier coverage.

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.