Microcode-programmable PowerQUICC III SoCs on the way

Oct 10, 2006 — by LinuxDevices Staff — from the LinuxDevices Archive — 5 views Freescale is readying its first PowerQUICC III SoCs (system-on-chip processors) to feature microcode-programmable QUICC engines. The MPC8568E and MPC8567E will clock up to 1.33GHz, and target 3G/WiMAX/LTE (“long-term evolution”) basestations, RNCs (radio network controllers), gateways, and ATM/TDM/IP equipment,… according to the company.

Freescale is readying its first PowerQUICC III SoCs (system-on-chip processors) to feature microcode-programmable QUICC engines. The MPC8568E and MPC8567E will clock up to 1.33GHz, and target 3G/WiMAX/LTE (“long-term evolution”) basestations, RNCs (radio network controllers), gateways, and ATM/TDM/IP equipment,… according to the company.

Freescale says the MPC8568E and MPC8567E will help broadband access equipment makers produce devices in which control- and data-path functions are handled by a single processor, reducing bill-of-materials and operational power costs. The chips can deliver up to 3K Dhrystone MIPS (millions of instructions per second), the company claims, and were designed specifically to address increasing broadband access equipment performance requirements.

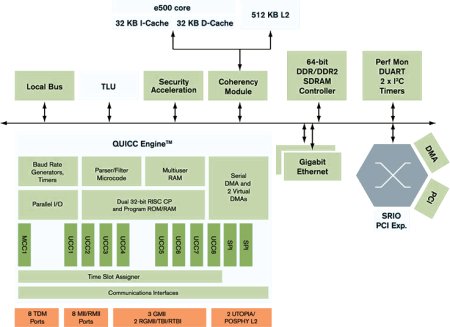

The MPC8568E and MPC8567E will be produced using 90nm silicon-on-insulator (SOI) process technology. They are based on Freescale's venerable e500 PowerPC core, clocked between 800MHz and 1.33GHz, along with 512KB of L2 cache. The e500 has long been supported under Linux.

The MPC8568E and MPC8567E are the first PowerQUICC III-series chips to integrate Freescale's microcode-programmable QUICC Engine, described as a “programmable system-on-chip (SoC) function block that accelerates communications protocols such as ATM, POS, Ethernet, PPP, HDLC, and TDM.”

MPC8568E and MPC8567E function block diagram

(Click to enlarge)

I/O includes a variety of high-speed system interfaces, including gigabit Ethernet (MPC8568E only), PCI express (8x for the MPC8568E, 4x for the MPC8567E), and Serial RapidIO interconnects to high-speed switches, FPGAs (field-programmable gate arrays), ASICs (application-specific integrated circuits), and DSPs (digital signal processors).

Additional integrated features include a Table Lookup Unit (TLU, MPC8568E only), a DDR1-2 memory controller, hardware acceleration for double precision floating point, and a high performance security engine that accelerate DES/3DES, AES, ARC-4, Kasumi, MD5, SHA1/2, RSA, and Elliptic Curve, enabling up to 1Gbps throughputs for IPSec, SSL/TLS and 3GPP security protocols, Freescale claims.

The new PowerQUICC III SoCs will ship with QUICC Engine microcode for standard functions. They will be available with a “modular development system” (MDS) that includes CodeWarrior development tools, and a reference board based on the AMC (advanced mezzanine card) form-factor.

Additionally, third parties are expected to offer RTOS support, compilers, debuggers, simulators, reference designs, and custom microcode for the MPC8568E and MPC8567E devices, Freescale says.

Jeff Timbs, director of marketing, stated, “The combination of ultra-high performance, multiple system interface options, and QUICC Engine technology provides outstanding price-to-performance ratios.”

Linley Group senior analyst Joseph Byrne, author of A Guide to Access Processors, stated, “The transition to packet-based networks and deployment of IP-based services is reshaping wireline and wireless access. The transition, however, is gradual instead of instantaneous. Communications equipment makers, therefore, need to deliver systems that are cost-effective, powerful, and capable of handling both legacy and IP protocols. To address these needs, these PowerQUICC III processors integrate a variety of high-speed interfaces and fast processors, including — uniquely — a 1.33GHz e500 core.”

Availability

The MPC8568E and MPC8367E are expected to sample in Q1, 2007. Pricing will start at $100.80 in 10K quantities.

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.