4G SoC offers 26 processors and Linux BSP

Jan 25, 2010 — by Eric Brown — from the LinuxDevices Archive — 72 viewsMindspeed announced a system-on-chip family designed for mobile broadband 3G/4G basestations, including femtocells and macrocells. Mindspeed's Transcede SoCs, starting with the 600MHz T4000 and 750MHz T4020, integrate dual ARM Cortex-A9 processors, 10 DSPs from Ceva, plus 10 DSP accelerators, and come with Linux BSPs, says the company.

The Transcede system-on-chip (SoC) is intended to replace the "inflexible" combinations of digital signal processors (DSPs), field programmable gate arrays (FPGAs), and network processing units (NPUs) that are often used in wireless basestations, says Mindspeed. It's claimed that whereas current, multi-component 3G+ and 4G basestation designs cost about $1,000 per blade and consume 100 watts of power, systems based on Transcede processors can cost under $300 per blade and consume less than 15 Watts, claims the company.

The Transcede platform is said to support single- and multi-sector basestations using the following wireless standards:

- Wideband code-division multiple access (W-CDMA) NodeB systems

- Long term evolution (LTE) frequency division duplex (LTE-FDD)

- LTE time-division duplex (TD-LTE, in China)

- Time-division synchronous code division multiple access (TD-SCDMA, in China)

- WiMAX 802.16d, 16e, and 16m standards

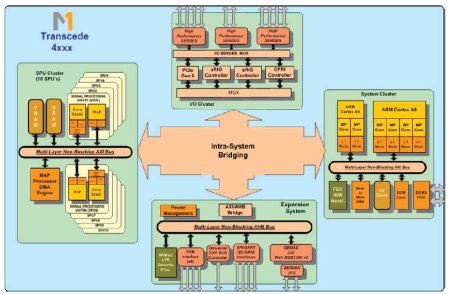

Transcede architecture

(Click to enlarge)

All-told the Transcede models incorporate 26 processors, including ten Ceva-X1641 DSPs from Ceva (see architecture diagram below). Each of the Ceva-X1641 DSPs integrate four MAC units and 16-bit data paths, with a mix of Very Long Instruction Word (VLIW) and Single Instruction Multiple Data (SIMD) architectures.

In addition, Mindspeed integrates its own accelerator chips for the DSPs. Other features include a security protocol accelerator, a FEC (front-end computer) hardware accelerator, and a multi-layer 64bit ARM AXI bus. A multi-layer internal microprocessor host bus supports non-blocking information flow between MAC and PHY, says the company.

Ceva-X1641 DSP architecture

(Click to enlarge)

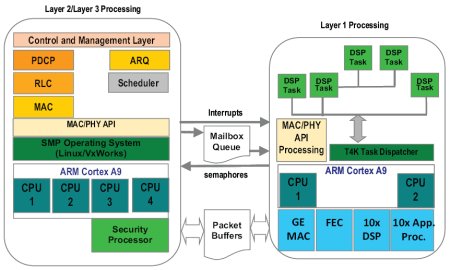

Linux BSP and reference design

A scalable hardware architecture is said to enable the use of the same Transcede software for picocells, microcells, and macrocells, as well as for future low-cost enterprise femtocell designs. The Transcede SoCs ship with software reference design that includes an open source Linux board support package (BSP), supporting software that runs across all the above platforms, says Mindspeed.

The reference design includes a standard physical-layer (PHY) implementation for LTE, WiMAX, and W-CDMA, with associated utilities and test scripts, says Mindspeed. Source code is available for all software deliverables, including executable documentation on the use of APIs and programming methods. The Transcede platform supports single-threaded programming languages like C and C++. In addition, the reference design kit also includes Mindspeed's task scheduler technology, which is said to simplify the programming model for DSP arrays.

Transcede software architecture

(Click to enlarge)

Stated Raouf Halim, CEO of Mindspeed, "We take our deep expertise in carrier-class, multi-core processing from our widely-deployed voice-over-IP platforms and extend it to key initiatives in the rapidly growing wireless-infrastructure market, especially in China and other high-growth markets. Manufacturers can now build a wide variety of platforms, from picocells to macrocells, that leverage the same Transcede device and Mindspeed's scalable software architecture."

Stated Alan Taylor, marketing director for Mindspeed's multiservice access business unit, "Transcede family devices can cut power consumption to less than 15 watts for sub-$300 blades, with significantly better performance, lower complexity, simplified programming and scalability, and a smaller footprint."

Availability

The Transcede T4000 and T4020 are available in sample quantities, with volume production scheduled to begin in the third quarter. The SoCs are packaged in a 31-millimeter-square flip-chip ball grid array (HFC-BGA). Pricing in OEM volumes of 10,000 units is $250 for the T4000 and $300 for the T4020. More information may be found here.

Mindspeed will be showcasing the Transcede family of products at the Mobile World Congress tradeshow in Barcelona, Spain, from Feb. 15-18, located at Hall 6, Stand 2J40.

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.