MIPS touts its quad-core IP as an Atom-beater

Sep 27, 2010 — by LinuxDevices Staff — from the LinuxDevices Archive — 4 viewsSunnyvale-based MIPS Technologies announced processor IP that will bring multiple cores to products such as digital TVs, STBs (set-top boxes), and Blu-ray players. Said to already have a “yet-to-be-announced lead licensee,” the MIPS32 1074K CPS (coherent processing system) provides up to four cores, a CM (coherence management) unit, a CPC (cluster power controller), and optional FPUs (floating point units), the company says.

According to MIPS, the new 1074k CPS is a development of its previously available 74K core, which has been licensed by more than 20 companies for STBs and other devices. Offered with or without floating point support, the 74K (block diagram, here) has a superscalar asymmetric dual-issue pipeline with out-of-order dispatch and completion. The core allows user-defined instruction set extensions ("CoreExtend") and works with a robust set of development tools including CodeSourcery, the company adds.

MIPS says it recently enhanced the 74K to deliver as much as 30 percent better performance on a variety of C++ applications, including web browsing and JavaScript. A single 74K core can now complete the popular Sunspider benchmark in well under two seconds, the company claims.

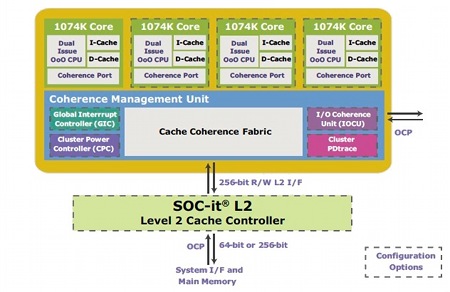

A block diagram of the 1074K CPS

(Click to enlarge)

As pictured above, the 1074K includes up to four of these newly enhanced 74K cores. The "complete, coherent multicore solution" also includes additional system components, described by MIPS as follows:

- coherence management (CM) unit — high-throughput coherence fabric supporting 256-bit wide buses internally on key datapaths, as well as external read and write data interfaces to L2 cache and through to rest of system logic

- I/O coherence unit (IOCU) — hardware acceleration for I/O coherence, offloading software implementation on CPUs

- cluster power controller (CPC) — multicore power gating, clock gating, and reset management

- global interrupt controller (GIC) — system and inter-processor interrupt controller

- EJTAG/PDtrace block for advanced debug/trace of complete coherent system

According to MIPS, an available 1074Kc version provides a coherent processing system using base integer cores. The 1074Kf version, meanwhile, adds a floating point unit in each core, offering IEEE 754 compliance and separate in-order, dual-issue pipelines.

Leaving an Atom in the dust …

The 1074K apparently does not offer multi-threading, as did the 1004K (block diagram, here) released by MIPS in 2008 as its first multicore product. (The 1004K now has more than ten licensees, says MIPS.)

Nonetheless, performance appears to be competitive. When compared to the single, hyper-threaded Atom CPU in Intel's CE4100 SoC, a three-core implementation of the 1074K CPS has a smaller silicon footprint and provides nearly 2.5x the performance as measured by the CoreMark benchmark, MIPS claims.

In a 40nm version produced using commercially available standard cell libraries from TSMC and memories from Dolphin Technology, the 1074K CPS will approach production frequencies of 1.5 GHz, MIPS says. An example dual-core implementation would have the following characteristics, the company adds:

- Peformance @ 1.25GHz:

- > 6,300 total CoreMark

- 5,000 total DMIPS

- Power — < 1W dynamic power

- Area — 4.1 x 4.1mm

As suggested earlier in this story, the 1074K CPS is primarily aimed at devices such as digital televisions, Blu-ray players, and STBs. But MIPS adds that the platform is "also targeted for home/wireless networking products as well as tablet computers."

Android was specifically cited as an operating system platform for the latter, but the 1074K CPS is said to run any MIPS32-compatible software, which would include Linux and Windows CE. At CES in January of this year, MIPS showed off a number of Android-based set-top box designs from its partners using MIPS-based Sigma Designs processors.

The 1074K CPS core is supported by tools from CodeSourcery, CriticalBlue and others, including MIPS Technologies' own development tools and probes, and symmetric multiprocessing (SMP) versions of Linux, MIPS adds.

MIPS says it will also provide accurate and fast simulation models for the 1074K CPS. SoC developers can leverage 100-percent cycle-accurate models — built with technology from Carbon Design Systems — for verification in SystemC and co-simulation environments. Software developers can also take advantage of fast instruction set simulators, developed in conjunction with Imperas, for use in software development and virtual platforms, the company adds.

Joseph Byrne, an analyst at The Linley Group and author of A Guide to CPU Cores and Processor IP, is quoted as saying, "We are seeing increasing adoption of multicore solutions across embedded markets as SoC manufacturers hit the limits of the performance a single CPU core can achieve. Based on MIPS' synthesis numbers, the 1074K CPS appears to be one of the best multiprocessor IP cores in terms of power and performance. And, putting three cores of this performance level into an area smaller than one Intel Atom CPU presents a compelling value proposition."

Further information

MIPS says the 1074K CPS will be "generally available" in October, including both the basic 1074Kc version and the floating-point-equipped 1074Kf version. More information may be found on the company's website, here.

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.