NEWS FLASH! 2nd-gen soft-core RISC processors run uClinux

May 19, 2004 — by LinuxDevices Staff — from the LinuxDevices Archive — 20 views Altera has announced a new family of 32-bit soft RISC processor cores it hopes will greatly expand the market appeal for its field-programmable gate arrays (FPGAs). The new Nios II cores support uClinux, and target software-intensive custom processor designs where application-specific integrated circuits (ASICs) would be… too costly and time-consuming to produce. The cores are available with a development kit that includes an Eclipse-based integrated development environment (IDE) for software development, as well as a development board (pictured).

Altera has announced a new family of 32-bit soft RISC processor cores it hopes will greatly expand the market appeal for its field-programmable gate arrays (FPGAs). The new Nios II cores support uClinux, and target software-intensive custom processor designs where application-specific integrated circuits (ASICs) would be… too costly and time-consuming to produce. The cores are available with a development kit that includes an Eclipse-based integrated development environment (IDE) for software development, as well as a development board (pictured).

Soft cores aim to reduce the cost, complexity, and power requirements of embedded processors by enabling designers to add custom peripheral mixes directly inside the processor chips, along with custom logic circuits, resulting in a more integrated, purpose-built design. The Nios II cores feature an automatically generated “Avalon Switch Fabric” interconnect.

Altera says that the original Nios cores “proved the soft core concept,” but that its new Nios II core family can deliver four times the performance at a quarter of the cost (as low as 35 cents per core). The company believes its FPGAs and royalty-free cores compare favorably in cost to ASICs, which it says have doubled in cost with the move from 0.18 to 0.13 micron and 90 nanometer processes.

The Nios II cores

The Nios II core family includes three core versions — Speed, Economy, and Standard — that can be implemented in single or multiple configurations on processors ranging from 2,910 to 179,400 logic elements. The Economy version delivers just over 20 Dhrystone MIPS (DMIPS) with a footprint of just over 500 logic elements, while the Performance version delivers over 200 DMIPS in just over 1K of logic elements. The graph below compares the three new Nios II cores with the two older Nios cores:

(Click to enlarge)

All three Nios II cores use the same instruction set, resulting in binary compatibility that enables customers to easily upgrade or downgrade, should their performance or power needs change. Differences among the Nios II cores are shown in the chart below.

(Click to enlarge)

The cores use a 32-bit instruction set architecture and a 32-bit data path, along with 32 general purpose registers and three instruction formats. They include separate instruction and data caches, and on-chip hardware for multiply, shift, and rotate. They support 256 user-defined instructions, and both fixed and variable cycle operation. User logic can be called as a C subroutine, and the Nios II IDE includes a user logic import wizard.

The cores can include (optionally) a single JTAG UART, enabling device configuration, code download, debugging, target STDIO (printing), and Flash programming over a single JTAG connection. They also include (optionally) a CompactFlash interface supporting True IDE mode and CompactFlash mode. The CF interface supports a low-level API, as well as the uClinux file system.

The Nios II cores support extremely simple, low-power designs, as well as complex, multiprocessor, software-intensive “system-on-programmable-chip” (SOPC) applications, as shown in the chart below.

(Click to enlarge)

According to Altera, custom instructions can increase the speed of a custom CRC algorithm operating on 64K of data by 27 times. Additionally, hardware acceleration can be added, resulting in performance over 500 times faster. The company cites a more real-world example of a custom hardware acceleration engine increasing the performance of an algorithm used in a 3G wireless communications device by ten times.

A Linux kernel port to Nios II performed by Microtronix and based on the Linux 2.6 source tree will be available for download from the Nios II website soon, according to Altera.

Nios II development kit

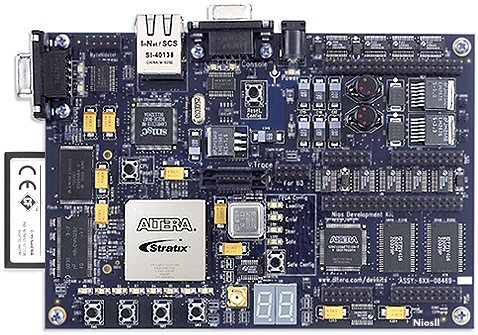

Nios II development kits are currently available for $995, on either Altera's Stratix or Cyclone FPGAs. The kits include the Nios II family of cores, the Eclipse-based Nios II IDE, a library of standard peripherals, a custom peripherals design tool (Altera's Quartus II tools with SOPC Builder — hosts only on Windows), a network protocols library, a development board (shown below), cables and accessories (including “USB Blaster” — see below), hardware and software reference designs (for Nios on Stratix), a year of free upgrades, and a 20 percent discount on Altera's training courses.

Altera lists the following features for the development board:

- Stratix EP1S10F780 device or Cyclone EP1C20FC400 device

- MAX EPM7128AE CPLD configuration control logic

- SRAM (1 Mbyte in two banks of 512 Kbytes, 16-bit wide)

- SDR SDRAM (16 Mbytes, 32-bit wide)

- Flash (8 Mbytes)

- CompactFlash connector header for Type I CompactFlash cards (40 available user I/O pins)

- 10/100 Ethernet physical layer/media access control (PHY/MAC)

- Ethernet connector (RJ-45)

- Two serial connectors (RS-232 DB9 port)

- Two 5-V-tolerant expansion/prototype headers (2 x 41 available user I/O pins)

- Two Joint Test Action Group (JTAG) connectors

- Mictor connector for debugging

- Four user-defined push-button switches

- Eight user-defined LEDs

- Dual 7-segment LED display

- Power-on reset circuitry

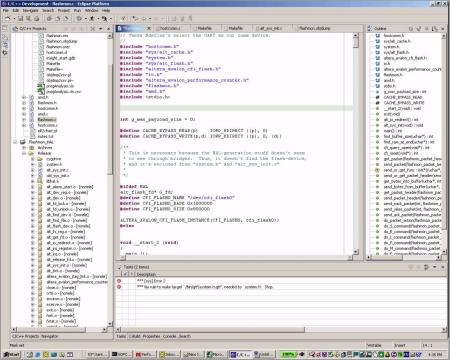

The Eclipse-based Nios II IDE (screenshot below) supports target connections via JTAG or through an instruction set simulator. It includes ModelSim design software. It supports advanced hardware debug features that include hardware JTAG debugging, hardware break points, data triggers, on-chip trace, and FS2 trace probing. It also offers flash memory programming tools.

(Click to enlarge)

The library of standard peripherals includes a JTAG UART and CompactFlash interface (as noted above); Interface to user logic; UART; interval timer; Parallel I/O (PIO); Serial Peripheral Interface (SPI); DMA controller; SDRAM controller; memory interfaces for on-chip ROM, RAM, and more; and an Ethernet port.

The protocols library includes a small footprint open source TCP/IP stack supporting IP, ICMP, UDP, and TCP, and a Berkeley Sockets API.

And here's something very cool: Altera even provides an optional USB-to-JTAG converter gizmo that let's you access the development board's JTAG inputs from a USB port on your host system. The “USB Blaster” can be used to program the FPGA and to debug the Nios II CPU. This programming cable is shipped as a part of the Nios II Kit.

Real Linux coming?

Asked whether Altera had any plans to develop an MMU function that could be added alongside the Nios II to enable the soft-core to run “real” Linux, a spokesperson said yes, it's on the roadmap. Don't hold your breath, though, as it's likely to be at last a year down the road.

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.