FPGAs to be integrated with ARM and MIPS cores, Altera says

Oct 22, 2010 — by LinuxDevices Staff — from the LinuxDevices Archive — 8 viewsAltera announced that it has licensed ARM's Cortex-A9 core, and will incorporate it into a 28nm chip integrating FPGA (field programmable gate array) technology during 2011. Meanwhile, a soft processor core based on MIPS Technologies MIPS32 architecture will be released earlier in the year, the company added.

The collaborations with ARM and MIPS were announced as part of what Altera is calling its "embedded initiative." As part of this, the company stated, it will "expand its current embedded partner programs by embracing the broad ecosystems from ARM, Intel and MIPS Technologies, as well as the FPGA world. In addition, Altera will collaborate with these entities to enhance the design flow and allow access to the growing number of FPGA-enabled embedded processing choices."

Altera says it signed an agreement with ARM earlier this year "to license a range of technologies, including the Cortex-A9 microprocessor." Future products will integrate hardened Cortex-A9 processor-based subsystems with 28nm FPGA technology, the company added.

According to Altera, it will also introduce a MP32 soft processor core based on MIPS Technologies' MIPS32 processor architecture in early 2011.

In a statement, the company said "the MP32 is a result of close collaboration between Altera, MIPS Technologies and lead customers over the past year. It will complement Altera's Nios II embedded processor and the portfolio of partner soft CPUs available for Altera devices, and significantly extend the number of operating systems and the amount of application code available for use on FPGAs."

In its release, Altera also referenced Intel's earlier announcement that it will offer the Atom E600 paired with an Altera FPGA (field programmable gate array) on a multi-chip package codenamed "Stellarton." That combination "provides additional flexibility for customers who want to incorporate proprietary I/O or acceleration, and enables developers to differentiate their designs by reacting quickly to changing requirements," the chipmaker said in September.

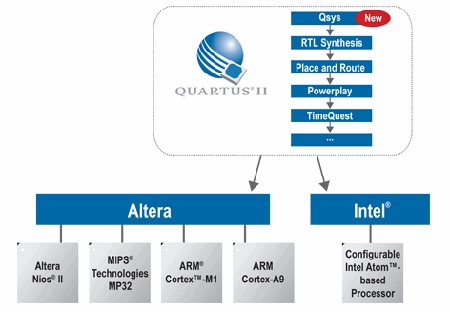

According to Altera, its upcoming Qsys system integration tool — part of the company's Quartus II design software — will allow developers to "apply our single design flow to a diversity of processors. These will include the forthcoming FPGA-enabled ARM and MIPS devices, Intel's "Stellarton," and Altera's own Nios II embedded processor, the company adds.

Altera's Quartus II and Qsys

Qsys (above), scheduled for delivery later this quarter, will offer "memory-mapped and datapath interconnects that achieve nearly double the performance of Altera's SOPC Builder tool, while being able to support industry-standard IP interfaces such as AMBA," the company says. The tool will also support hierarchical design, incremental compile, and partial reconfiguration methodologies, the company says.

Background

As an Electronics Weekly article by Richard Wilson notes, FPGAs have typically relied on lower-performance soft core processors such as the Nios II. Altera Senior Marketing Director Chris Balough is quoted as saying, "thirty percent of FPGAs shipped by us include a NIOS processor."

However, vendors have been moving towards integrating FPGAs with higher-performance CPUs, both to increase speed and because this makes the devices easier to program. Last April, Altera competitor Xilinx, which previously employed PowerPC-based processors in its FPGAs, announced that it, too, would combine its devices with Cortex-A9 cores.

In March, ARM announced version 4 of its AMBA (advanced microprocessor bus architecture), billed as an open standard, on-chip interconnect specification for the connection and management of functional blocks on a SoC (system on chip). Whereas ARM's MPCore handles communications among Cortex-A9 cores, AMBA handles interaction with other processors, memory, and peripherals.

According to ARM, AMBA promotes design re-use by defining a common backbone for SoC modules using specifications for AXI, AHB, APB, and ATB, says ARM. Version 4 of the spec added three new interface protocols: an AXI4 protocol for improving performance and power efficiency, plus AXI4-Lite and AXI4-Stream, both specifically optimized for FPGAs.

AXI4-Lite is designed for communications with simpler, smaller control register-style interfaces. AXI4-Stream, meanwhile, is designed for unidirectional data transfers from master to slave "with greatly reduced signal routing," says ARM.

Asked by Electronics Weekly's Wilson if ARM would adopt the AXI4 bus, Balough reportedly responded, "We'd be fools not to."

Subsequent to the announcement of its embedded initiative, Altera announced record third quarter results. On Oct. 19, it said third quarter sales reached $527.5 million, up 12 percent from the second quarter of 2010 and up 84 percent from the third quarter of 2009. New product sales increased 24 percent sequentially, the company added.

John Daane, Altera's president, chief executive officer, and chairman of the board, stated, "The 53 percent sequential growth we saw in our 40nm FPGAs demonstrates the attractiveness of Altera's FPGAs in today's marketplace. We are in the final stages of development for our initial 28nm FPGAs and believe that the unique architectural features and performance we offer will extend our current 40nm technology leadership to this next process node."

Further information

More information about Altera's Quartus II design software and upcoming Qsys tool may be found on the company's website, here. More information about ARM's AMBA may be found here.

The Electronics Weekly article by Richard Wilson referred to in this story can be found here.

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.