PICMG 1.3 SBC sports 3.2GHz dual-core Pentium D, runs Linux

Apr 14, 2006 — by LinuxDevices Staff — from the LinuxDevices Archive — 12 views IEI Technology claims its new PICMG 1.3-compliant single-board computer (SBC) is the first to use an Intel Pentium D dual core processor. The PCIE-9450 supports processor clock rates up to 3.2 GHz at front-side bus speeds up to 1.066 GHz, and runs Linux, according to the company.

IEI Technology claims its new PICMG 1.3-compliant single-board computer (SBC) is the first to use an Intel Pentium D dual core processor. The PCIE-9450 supports processor clock rates up to 3.2 GHz at front-side bus speeds up to 1.066 GHz, and runs Linux, according to the company.

In addition to its impressive processor specs, the PCIE-9450 provides four 240-pin DDR2 DIMM sockets that accommodate up to 4 GB of SDRAM, according to IEI. Four serial ATA II ports, together with Intel's Matrix Storage Technology, support RAID levels 1, 5, and 10. Seven USB 2.0 ports provide peripheral connectivity. The board also includes a display controller, as well as audio, floppy, serial, and parallel interface ports.

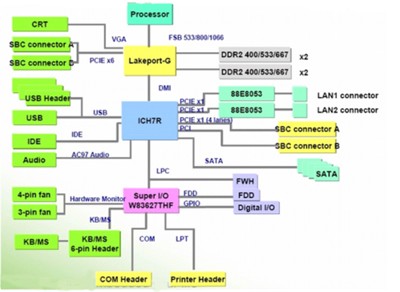

PCIE-9450 Block Diagram

(Click image for larger view)

IEI lists the following key features and specifications for the PCIE-9450:

- Processor:

- Intel Pentium 4 or Pentium D 8xx, LGA775 socket

- Intel 945G Express chipset and ICH7R southbridge

- Memory — up to 4 GB DDR2 SDRAM, at up to 667 MHz

- Display — Intel Graphics Media Accelerator 950 integrated with chipset; 15-pin VGA out

- Storage:

- 4 SATA II with Raid 0,1,5 and 10 support

- ATA 100

- I/O ports:

- 2 PCIE Gigabit Ethernet

- 7 USB 2.0 (6 via pin header)

- 2 serial

- IrDA

- LPT, PS/2 keyboard and mouse

- 4 each digital in and out on two 5-pin headers

- Expansion:

- PCI Express — 6 1-lane, 1 4-lane

- 32-bit PCI bus

- Power — Pentium D 3.73GHz/1066 MHz CPU with 4GB DDR2-667MHz

- +12V — 9 A

- +5V — 2.6A

- +3.3V — 6.3A

- +5Vsb — 0.93A

- -12V — 0.1A

About PICMG 1.3

PICMG 1.3 is the latest in a series of System Host Board (SHB) specifications from the PCI Industrial Manufacturers Group that adapts the popular desktop PC format to passive backplane implementations required in more demanding environments such as industrial automation, military, medical, and telecom.

The original PICMG 1.0 defined pinouts for the ISA (original PC/AT bus) and parallel PCI buses to the backplane. PICMG 1.2 added support for PCI-X. PICMG 1.3 addresses the bandwidth issues created by contemporary processors, by substituting PCI Express for the parallel buses.

PICMG 1.3 defines four backplane connectors, labeled A through D in the above photo:

- A — 164 pins — PCI Express up to 16 lanes

- B — 98 pins — PCI Express up to 8 lanes

- C — 164 pins — SATA, USB, IPMB, SMBUS, Geographic addressing, Power management

- D — 98 pins (optional) — PCI or PCI-X parallel bus.

PICMG 1.3 was ratified in August of last year.

Availability

The company did not disclose delivery or pricing information.

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.