3M, IBM collaborate on chip stacking

Sep 7, 2011 — by LinuxDevices Staff — from the LinuxDevices Archive — 1 viewsIBM and 3M announced they'll work together to develop adhesives that will help package semiconductors into dense towers of silicon. By including up to 100 layers, the resulting chips could be up to 1,000 faster than today's speediest microprocessors, the companies claim.

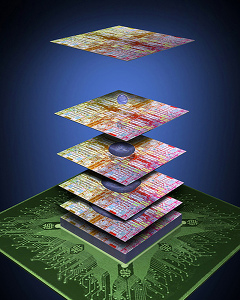

In a Sept. 7 statement, 3M and IBM said their work "can potentially leapfrog today's current attempts at stacking chips vertically — known as 3D packaging. The joint research tackles some of the thorniest technical issues underlying the industry's move to true 3D chip forms. For example, new types of adhesives are needed that can efficiently conduct heat through a densely packed stack of chips and away from heat-sensitive components such as logic circuits."

Adhesives could allow future chips to include up to 100 layers of silicon

Source: IBM

(Click to enlarge)

According to 3M and IBM, today's packaging and bonding techniques for semiconductors can only be applied to individual chips, a process "akin to frosting a cake slice-by-slice." In contrast, the companies added, they plan to develop adhesives that can be applied to silicon wafers, "coating hundreds or even thousands of chips at a single time."

However, the partners neither described any progress on their research to date, nor provided a timetable for the development of any commercial products. (It seems to us that no matter how thermally conductive an adhesive is, cooling 100 layers of silicon would be a challenge, to say the least.)

Intel, meanwhile, has said it will incorporate 3D "Tri-Gate" technology in its "Ivy Bridge" Core processors, scheduled to enter production by the end of this year.

While it's less ambitious than what 3M and IBM are discussing, Tri-Gate replaces the flat conducting channels on a silicon wafer with 3D "fins" that rise up vertically from the substrate. By allowing more current to be conducted and providing faster switching, this modification preserves performance while cutting power consumption by more than 50 percent, according to the chipmaker. (For more background, see our previous coverage.)

"Today's chips, including those containing '3D' transistors, are in fact 2D chips that are still very flat structures," charged Bernard Meyerson, vice president of research at IBM. "Our scientists are aiming to develop materials that will allow us to package tremendous amounts of computing power into a new form factor — a silicon 'skyscraper'."

Herve Gindre, division vice president for 3M's Electronics Markets Materials Division, stated, "Capitalizing on our joint know-how and industry experience, 3M looks forward to working alongside IBM — leader in developing pioneering packaging for next-generation semiconductors. We are very excited to be an integral part of the movement to build such revolutionary 3D packaging."

An animation illustrating future towers of silicon

Source: IBM

(click to play)

Further information

More information about adhesives currently produced by 3M's Electronic Markets Materials Division may be found on the company's website.

Jonathan Angel can be reached at [email protected] and followed at www.twitter.com/gadgetsense.

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.