IBM and Micron unveil 3D RAM

Dec 6, 2011 — by LinuxDevices Staff — from the LinuxDevices Archive — 2 viewsIBM and Micron say they'll collaborate to create a 3D memory chip that uses vertical TSV (through-silicon via) conduits, for speeds 15 times faster than today's technology. Meanwhile, Micron and Intel announced the “world's first” 20nm, 128Gbit MLC (multi-level-cell) flash device as well as mass production of a 64Gbit version.

With modern circuit boards getting more pressed for available real estate than Manhattan, designers have been looking for ways to spread their silicon up, not out. In September, for example, IBM announced that it is working with 3M to develop adhesives that will help package semiconductors into towers of silicon with up to 300 layers.

In a related development, IBM fellow Subu Iyer (pictured) used this week's IEEE International Electron Devices Meeting to present what the company describes as a "manufacturing breakthrough." It involves the creation of TSVs, vertical conduits that can connect individual DRAM chips in a stack.

In a related development, IBM fellow Subu Iyer (pictured) used this week's IEEE International Electron Devices Meeting to present what the company describes as a "manufacturing breakthrough." It involves the creation of TSVs, vertical conduits that can connect individual DRAM chips in a stack.

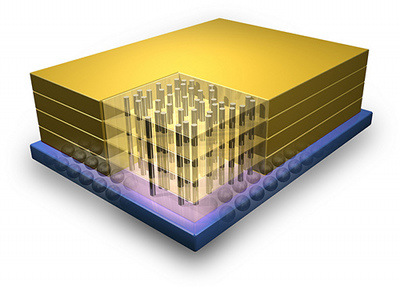

Artist's conception of a Hybrid Memory Cube

(Click to enlarge)

According to IBM and Micron, the TSVs allow the creation of Hybrid Memory Cubes (above), which deliver "bandwidth and efficiencies a leap beyond current device capabilities." Prototypes have offered bandwidth of 128 Gbits/sec., compared to the 2.8 Gbits/sec. offered by current state-of-the-art devices, the companies say.

It's claimed HMC memory devices will occupy just ten percent of the footprint of conventional memory. Further, they'll need 70 percent less energy, IBM and Micron add.

The companies said in a statement that HMC parts will be manufactured at IBM's advanced semiconductor fab in East Fishkill, New York, using 32nm high-K metal gate process technology, From there, they'll be shipped off to one of Micron's 300mm fabs in Boise, Idaho, where they will be mated with stacked memory modules and TSV pipelines etched by Micron, a Dec. 1 article in The Register added.

Iyer stated, "This is a milestone in the industry move to 3D semiconductor manufacturing. The manufacturing process we are rolling out will have applications beyond memory, enabling other industry segments as well. In the next few years, 3D chip technology will make its way into consumer products, and we can expect to see drastic improvements in battery life and functionality of devices."

The IBM/Micron release did not say when HMC-based DRAM will hit the market. According to Timothy Prickett Morgan's story for The Register, however, it will go on sale during the second half of 2013.

Meanwhile, Iyer is scheduled to moderate a panel discussion titled "Is 3-Dimensional Integration at Best a Niche Play?" this evening (Dec. 6) at the IEEE International Electron Devices Meeting in Washington, D.C. Intended to evolve into a "passionate discussion with some serious audience participation," according to the organizers, the event will include the following panelists:

- Jan Vardaman, Techsearch, Inc.

- John Lau, ITRI

- Shekhar Borkar, Intel

- Sitaram Arkalgood, Sematech

- SiYoung Choi, Samsung

Intel, meanwhile, has said it will incorporate 3D "Tri-Gate" technology in its "Ivy Bridge" Core processors, expected to start appearing next April. Tri-Gate replaces the flat conducting channels on a silicon wafer with 3D "fins" that rise up vertically from the substrate.

By allowing more current to be conducted and providing faster switching, Tri-Gate preserves performance while cutting power consumption by more than 50 percent, according to the chipmaker. (For more background, see our previous coverage.)

New NAND flash devices

On a more workaday level — where there's competition from Toshiba and Samsung, for example — Micron also had a Dec. 6 announcement to make with Intel. This one concerns the IM Flash Technologies (IMFT) joint venture's development of the "world's first" 20nm, 128Gbit MLC NAND flash device.

According to the companies, the 128Gbit device will allow the creation of 1TB of storage in a fingertip-size package by using just eight dies. It will achieve speeds of 333 megatransfers per second (MT/s), "providing customers with a more cost-effective solid-state storage solution for today's slim, sleek product designs, including tablets, smartphones and high-capacity solid-state drives (SSDs)."

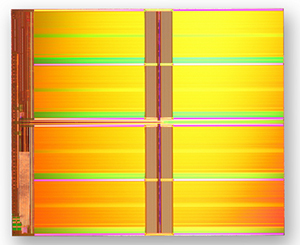

The Intel/Micron 20nm flash die

(Click to enlarge)

Intel and Micron added that the key to their success with 20nm process technology has been a new planar cell structure. "The first in the industry," this "successfully breaks the scaling constraints of the standard NAND floating gate cell by integrating the first Hi-K/metal gate stack on NAND production."

It's said the new Intel/Micron 128Gbit MLC device will begin sampling in January, entering mass production during the first half of 2012. Meanwhile, a previously announced 64Gbit 20nm NAND is available in quantity now, the companies added.

Jonathan Angel can be reached at [email protected] and followed at www.twitter.com/gadgetsense.

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.