SoC has dual ARM Cortex-A9 cores

Jul 29, 2010 — by LinuxDevices Staff — from the LinuxDevices Archive — 22 viewsSTMicroelectronics (ST) announced an SoC (system on chip) claimed to be the industry's first to combine two ARM Cortex-A9 cores with a DDR3 memory interface. The SPEAr1310 offers dual cores clocked at 600MHz, gigabit Ethernet, plus connectivity including USB, SATA, and PCI Express, the company says.

ST's SPEAr1310 is the first member of a SPEAr1300 product line that was announced in May, and which will include one or more additional SoCs, according to the company. The SPEAr1300 architecture is touted as offering "industry-leading performance in terms of DMIPS/MHz and power consumption/DMIPS ratios, in addition to cost efficiency and customizability advantages."

ST says the SPEAr1310 offers dual ARM Cortex-A9 processors, clocked at up to 600MHz per core, for an equivalent of 3000 Dhrystone MIPS. The SoC will be manufactured in ST's low-power, 55nm HCMOS process technology, the company adds.

According to ST, the SPEAr1310 includes both an integrated DDR3 memory controller plus a "full set of connectivity peripherals." The device targets "high-performance embedded-control applications across market segments from communication and computer peripherals to industrial automation," the company adds.

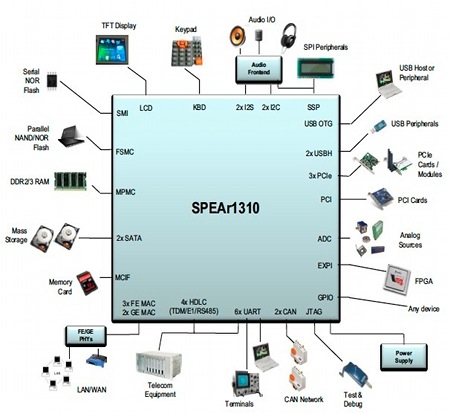

A diagram of the SPEAr1310's external connectivity

(Click to enlarge)

ST says the SPEAr1310's dual cores — each equipped with a 32KB L1 cache and a shared 512KB L2 cache — will support both symmetric (SMP) and asymmetric (AMP) multiprocessing. Equipped with a 32KB BootROM and 32KB of internal static RAM, the device has a DDR2/DDR3 memory controller that can address up to 1GB of RAM, the company adds.

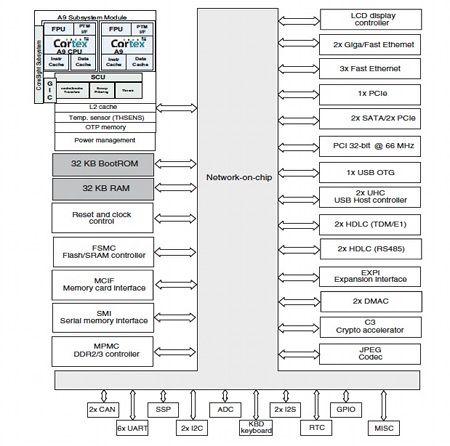

A block diagram of the SPEAr1310's internal connectivity

(Click to enlarge)

Connectivity on the SPEAr1310 is said to include the following:

- 2x gigabit/Fast Ethernet ports (for external GMII/RGMII/MII PHY)

- 3x fast Ethernet (for external SMII/RMII PHY)

- 3x PCIe 2.0 links (embedded PHY)

- 2x SATA gen-2 host port (alternative to two PCIe)

- 1x 32-bit PCI expansion bus (up to 66MHz)

- 2x USB 2.0 host ports with integrated PHYs

- 1x USB2.0 OTG port with integrated PHY

- 2x CAN 2.0 a/b interfaces

- 2x TDM/E1 HDLC controllers with 256/32 time slots per frame respectively

- 2x HDLC controllers for external RS485 PHYs 2x I2S ports for external audio/modem

- 6x UARTs (up to 5Mbaud)

- 1x SSP port (SPI and other protocols), master/slave, up to 41 Mbps

- 2x I2C ports master/slave

ST adds that the SPEAr1310 has an interface for four-wire resistive touchscreens, an LCD controller that supports resolutions up to 1920 x 1200 pixels, and a 9 x 9 keyboard controller. The devices's memory card interface supports SD/SDIO 2.0, SDHC, MMC 4.2/4.3, CF/CF+ Rev 4.1, and XD, the company says.

Among other miscellaneous features, the SPEAr1310 is said to have two high-performance, eight-channel DMA controllers, a 10-bit ADC, and programmable directional GPIO signals. A JTAG interface is included for testing and debugging, and there's an embedded sensor for monitoring junction temperatures, says ST.

According to ST, the SPEAr1310's Accelerator Coherency Port (ACP) and Network-on-Chip routing capabilities address "the latest application requirements for hardware acceleration and I/O performance." Available ECC (Error Correction Coding) protection "dramatically improves" MTBF, the company adds.

Loris Valenti, general manager of ST's computer systems division, stated, "[The] SPEAr1310 is the first device in the recently announced SPEAr1300 family and others will follow shortly. With its innovative architecture and powerful feature set, [the] SPEAr1310 is at the leading edge of the embedded processor market and enables an unprecedented mix of cost competitiveness, performance and flexibility."

Background

STMicroelectronics (ST) launched its SPEAr (structured processor enhanced architecture) range in 2005 with the release of the SPEAr Head200, integrating a 266MHz ARM926EJ-S core with a 200Kgate configurable logic block. The SPEAr Head600 and SPEAr Plus600 followed in 2007, using the same core and 90nm production process, but clocking up to 333MHz and sporting a 600Kgate configurable logic array.

In 2008, ST moved to a 65nm process with the SPEAr Basic, again with the 333MHz ARM926EJ-S core. This time with a 300Kgate logic array, the device was touted as facilitating custom design, thanks to a separately available development kit and an external FPGA (field programmable gate array).

Last February, the company added the SPEAr300, 310, 320, and 600, using the same ARM926EJS core and similar clock speeds — 333MHz "worst-case," or "up to 400MHz" in typical conditions. Fabbed with 90nm and 65nm technology, too, the SoCs omitted configurable logic arrays, instead providing on-chip functionality tailor-made for different market segments. (For more details, see our earlier coverage, here.)

Further information

Operating system support was not detailed for the SPEAr1310, and we noted mention of only Linux for the SPEAr300, 310, 320, and 600 SoCs. However, earlier SPEAr offerings were also said to support Windows CE.

According to ST, the SPEAr1310, supplied in a 23 x 23mm PBGA (plastic ball grid array), is sampling now to lead customers for evaluation and prototyping. Further information on the device may be found on the company's website, here.

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.