Via unveils “Nano” processors

May 28, 2008 — by LinuxDevices Staff — from the LinuxDevices Archive — 9 views Via Technologies has announced the first processors based on its new x86-compatible “Isaiah” micro-architecture. The “Nano” processors are pin-compatible with Via's existing C7 processor family, and occupy similar power and footprint envelopes, while doubling or quadrupling performance, Via claims.

Via Technologies has announced the first processors based on its new x86-compatible “Isaiah” micro-architecture. The “Nano” processors are pin-compatible with Via's existing C7 processor family, and occupy similar power and footprint envelopes, while doubling or quadrupling performance, Via claims.

(Click here for a larger view of the Via Nano)

digg this story |

Via will continue selling C7 and Eden chip lines, which are based on the company's Esther architecture. The new Nano parts add a much faster, yet still pin-compatible option for OEMs and motherboard vendors, Via says. Glenn Henry, CEO of Via's CenTaur processor division, explained, “The C7, our current product, is very mature, and very good at what it does. So, we thought, if we're going to do a new processor, we should push the performance up a lot.”

Both the Esther and Isaiah microarchitectures were designed by Via's Austin, Tex. based CenTaur chip unit, headed up by Henry, a former IBM engineering fellow. Prior to Isaiah, Esther and all of Via's previous architectures used in-order execution — similar to Intel's new Atom processors — for the lowest power and size requirements. Isaiah steps up to an out-of-order execution pipeline, similar to Intel's Core Duo architecture, while also adding support for the 64-bit architectures now used by Intel and AMD, for SSE-3 media processing instructions, and for Intel's VTX architecture for VMs (virtual machines). “We're already running the Linux kernel VM and Xen on it,” Henry boasted.

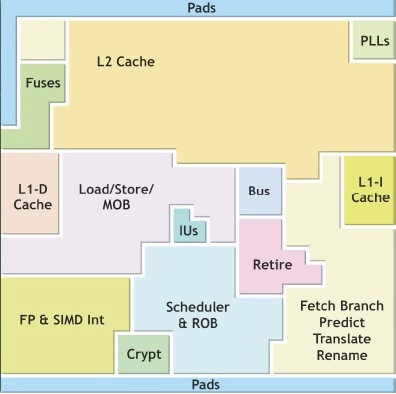

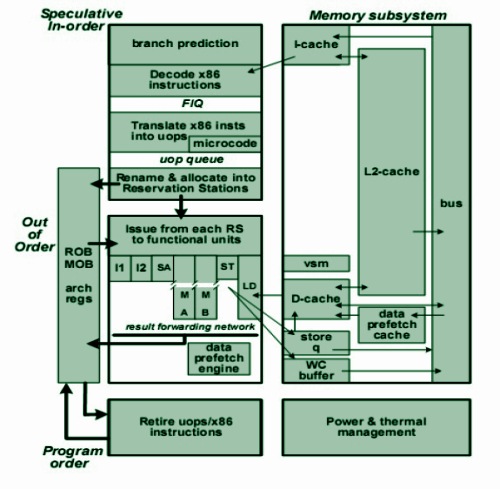

A block diagram of the Via Nano

The Nano processors, ranging in clock speeds from 1.0GHz to 1.8GHz, will be available in an L-series (“low-power”) for mainstream desktop and mobile PC systems, and in a U-series (“ultra-low-power”) for mini-notebooks and small form factor devices. Socket-compatible with C7 parts, they'll obviously use the same 21mm x 21mm nanoBGA2 package. However, Nano parts are being manufactured by Fujitsu using a 65nm process, rather than by IBM on 90nm process technology, as with the C7.

Henry said he expects Nano processors to outperform Intel's Atom chips, while offering greater compatibility with existing three-chip chipset designs. Observing that Atom chips work only with Intel's Poulsbo companion chip, a combination north-/south-bridge chip, he said, “We have two products that are plug-compatible. Intel has a totally different approach, with discreet products so that it does not cannibalize its high-margin products.”

Comparing a 1GHz C7 processor to the new 1GHz Nano, Henry said both could run fanlessly, with TDPs (thermal dynamic power) below about 5 Watts. Yet, he expects the Nano chip to perform 200 to 400 percent faster. “Performance will double on most things, with floating-point performance increasing three to four times. We worked on that a lot because, frankly, our multimedia performance [in Esther] was not that good,” Henry admits.

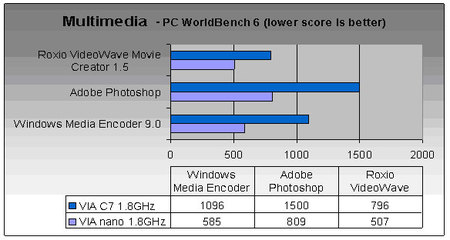

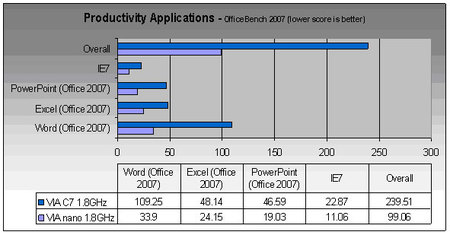

Noting that the Nano's power consumption is not drastically different from similarly clocked C7 parts, Via released figures suggesting that Nano chips perform significantly faster. For example, a 1.8GHz Nano was 2.4 times faster than a 1.8GHz C7 on the OfficeBench 2007 rating of Microsoft Office applications performance. Similarly, it ran 1.9 times faster running Adobe Photoshop filters and doing Windows Media encoding, as measured by the PC WorldBench 6 test. Finally, it ran the “ALU Power Performance” test in the SiSoft Sandra XIIc suite 3.2 times faster. The charts below, supplied by Via, tell the tale.

Various benchmark comparisons of Nano with other embedded processors

(Source: Via. Click any chart to enlarge)

Informal remarks aside, Via has mostly left the “dirty work” of benchmarking the Nanos against their Intel counterparts to others. However, the company claims that a 1.6GHz Nano, with a TDP of 17 watts, performs almost identically on the OfficeBench 2007 suite to a 1.6GHZ Intel Celeron M 520, with a TDP of 31 watts. This makes the Nano “the leading processor in terms of performance per Watt on the market,” the company says.

The Nano processor will initially be offered in five different versions, as listed in the chart below. Two “low voltage” versions, the L2100 and L2200, offer clock speeds of 1.8GHz and 1.6GHz, and maximum power consumptions of 25.5 and 17 Watts, respectively. Three “ultra low voltage” versions (the U2400, U2500, and U2300) offer TDPs ranging from 8 Watts down to 5 Watts, and idle power consumption of 100mW. All the parts support Via's 800MHz V4 frontside bus, have two 64KB L1 caches, and feature 1MB L2 caches with 16-way associativity, the company says.

| Product & Model Name | Clock Speed | VIA V4 Bus | Maximum Power (TDP Max) |

| VIA Nano L2100 processor | 1.8GHz | 800MHz | 25.5W |

| VIA Nano L2200 processor | 1.6GHz | 800MHz | 17W |

| VIA Nano U2400 processor | 1.3GHz | 800MHz | 8W |

| VIA Nano U2500 processor | 1.2GHz | 800MHz | 6.8W |

| VIA Nano U2300 processor | 1.0GHz | 800MHz | 5W |

The Via Nano comes in five different versions

Architecture

The Nano processors are the first 64-bit, superscalar, speculative out-of-order processors in Via's x86 platform portfolio, the company says. They can decode three full x86 instructions per clock, generate three fused (internal machine instructions) micro-ops per clock, issue (speculatively and out-of-order) seven execution micro-ops per clock to seven execution ports, and retire three fused microops per clock.

A conceptual diagram of Via's Nano architecture

As the above conceptual picture illustrates, the Nano processors include pipelines that fetch x86 instruction bytes and translate them into micro-ops. The x86 instructions and micro-ops proceed in program order down the top left (“in-order”) portion of the pipeline. The “speculative” label refers to the fact that the processor may not be actually fetching the correct program instructions (in cases of a branch misprediction, for example). “Out-of-order” issue and execution happens when the pipeline components take the translated micro-ops and issue them to the appropriate execution units. This happens whenever inputs are available, not necessarily in program order.

According to Via, the Nanos' L2 cache is designed to support a wide variety of sizes with minimal implementation effort. In addition, the L2 cache is “exclusive,” meaning that L1 cache contents do not reside in it. This effectively increases L2 cache size compared to “competitor architectures” with inclusive caches, Via says. At the same time, the architecture was designed for multi-core, multiprocessing friendliness, Via says.

Touting the Nano's “significant emphasis on high-performance floating-point execution,” Via says the processor can execute four floating-point adds and four floating-point multiplies every clock. A “completely new algorithm for floating-point results in the lowest floating-point add latency of any x86 processor,” the company said, in a whitepaper about the Isaiah architecture. In addition, the integer data path for SIMD integer (SSEx) instructions is 128-bits wide, and almost all SSEx instructions (including all shuffles) execute in only one clock.

All this means that the Nano processor can provide “exceptionally smooth playback of Blu-ray and other HD video formats,” with encrypted media streams of up to 40Mbps. When combined with an appropriate discrete graphics card, the Nano provides “silky smooth rendering of 3D images,” says Via.

Power consumption

As noted earlier, the Nano processors feature TDPs ranging from a high of 25.5 Watts, to a low of five Watts. In addition to “the latest x86 instruction-level power controls,” the CPUs include a new “C6” power state in which the caches are flushed, internal state is saved, and the core voltage is turned off, the company says.

Claiming that Intel CPUs must stop their bus and processor execution while changing from one P-state (performance/voltage state) to another, Via says the Nano can achieve such transitions while keeping everything running. Using another unique mechanism, the Nano can automatically adjust the P-state voltage based on the processor's die temperature, according to the company.

Availability

According to Via, Nano processors are available now for OEMs and motherboard vendors. Systems featuring the CPUs are expected to come to market in the third quarter. Since the parts are pin-compatible with C7/Eden processors, a wide array of development boards should support them, although Via has not yet announced any. Still, Via's marketing chief, Richard Brown, promised, “We'll see Mini-ITX boards around the Nano fairly quickly.”

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.