Open source ARM Cortex simulator models debut

Dec 8, 2010 — by Eric Brown — from the LinuxDevices Archive — 443 viewsImperas released open source simulations of ARM'S Cortex-M series of cores on its associated Open Virtual Platforms (OVP) site, with models for other ARM Cortex models expected to follow in the coming months. Imperas also announced that Cadence Design Systems is using Cortex-M and other Imperas and OVP models in some of its system design tools.

The Cortex-M processor core models and example platforms are available from the Open Virtual Platforms website, along with models of other ARM processors including the ARM7, ARM9, ARM10, and ARM11 families. All the models work with the open source OVP simulators (OVPsim), as well as more robust commercial simulators and development tools from Imperas, says the company.

The Cortex-M models are claimed to be "instruction accurate," and perform at hundreds of millions of instructions per second, says Imperas.

First up: Cortex-M3

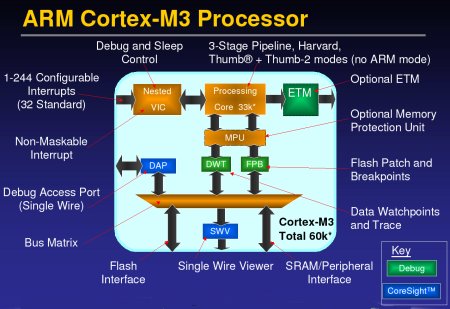

The initial Cortex-M model will be for the venerable Cortex-M3 core, says Imperas. Although the low-end workhorse Cortex-M series does not get the attention of its newer Cortex-A siblings, they are a central — and profitable — part of ARM's business.

ARM Cortex-M3 architecture

(Click to enlarge)

Most embedded developers will be more interested, however, in waiting for OVP core models for other ARM Cortex cores, which will be available within the next 16 weeks, says the company. Presumably, these will include simulators that can help take the bite out of exploring complex multicore SoCs such as the Cortex-A9.

OVP also offers reference virtual platforms incorporating some of its ARM cores, including bare metal platforms, as well as a virtual platform of an Atmel AT91SAM7 processor. In addition, it provides a virtual platform of the ARM IntegratorCP development board using the ARM926EJ-S core. The board is said to enable users to boot Linux in under 10 seconds on a 2GHz laptop using OVPsim.

Cadence collaboration on EDA360

The Cortex-M model and other OVP models will be used in an Imperas collaboration with Cadence as part of the latter's EDA360 "industry vision" for application-driven system development, says Imperas. Specifically, the collaboration involves EDA360's "System Realization" components.

As part of the collaboration, Imperas has joined the Cadence System Realization Alliance, and both Imperas and OVP and Imperas software development tools have been integrated with the Cadence Incisive Enterprise Simulator and Incisive Software Extensions products, says the company.

Stated Michai Siwinski, group director of product management for System Realization at Cadence, "Their Open Virtual Platforms technology, model creation tools and the large library of fast processor core models complements Cadence System Realization offerings to provide an effective solution for system and software development."

Stated Simon Davidmann, president and CEO, Imperas, and founding director of the OVP initiative. "OVP, with ultrafast simulation, accelerates the development cycle and makes debug easier for software engineers."

Background

Imperas launched OVP in March 2008, making much of its simulation and virtual prototyping technology — public and freely available, says the company. The technology includes free open source models, API documentation, and a downloadable simulator. OVP reference platforms are all available as source code, and can be easily modified to add or change the memory and peripheral components, says Imperas.

The OVP processor models are focused on supporting embedded software developers, especially those building hardware-dependent software such as firmware and bare metal applications, says Imperas. Virtual platforms utilizing these models can be created with the OVP peripheral and platform models, or the processor models can be integrated into SystemC/TLM-2.0 based virtual platforms using the native TLM-2.0 interface available with all OVP models, says the company.

In addition to working with the OVP simulator, which offers integration with the Eclipse IDE, the models work with Imperas' commercial tools for multicore software verification, analysis, and debug, says the company. These are said to include tools for software development on virtual platforms, including OS- and CPU-aware tracing, profiling, and code analysis tools.

Imperas has previously helped MIPS develop fast simulation models for its 1074K CPS core, as well as for its M14K and M14Kc cores. MIPS models are available from OVP, along with the aforementioned ARM models, plus models for Virage ARC, NEC, PowerPC, and openCores processors, says OVP.

All the platforms are available for Fedora Linux Core 4, and Windows XP Professional SP2 desktop systems, says the company.

Availability

The OVP simulators for ARM Cortex-M processors are available for free download at the OVPworld.org site, here. Imperas may be found at its website, here.

This article was originally published on LinuxDevices.com and has been donated to the open source community by QuinStreet Inc. Please visit LinuxToday.com for up-to-date news and articles about Linux and open source.